M59MR032CZC データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M59MR032CZC Datasheet PDF : 49 Pages

| |||

M59MR032C, M59MR032D

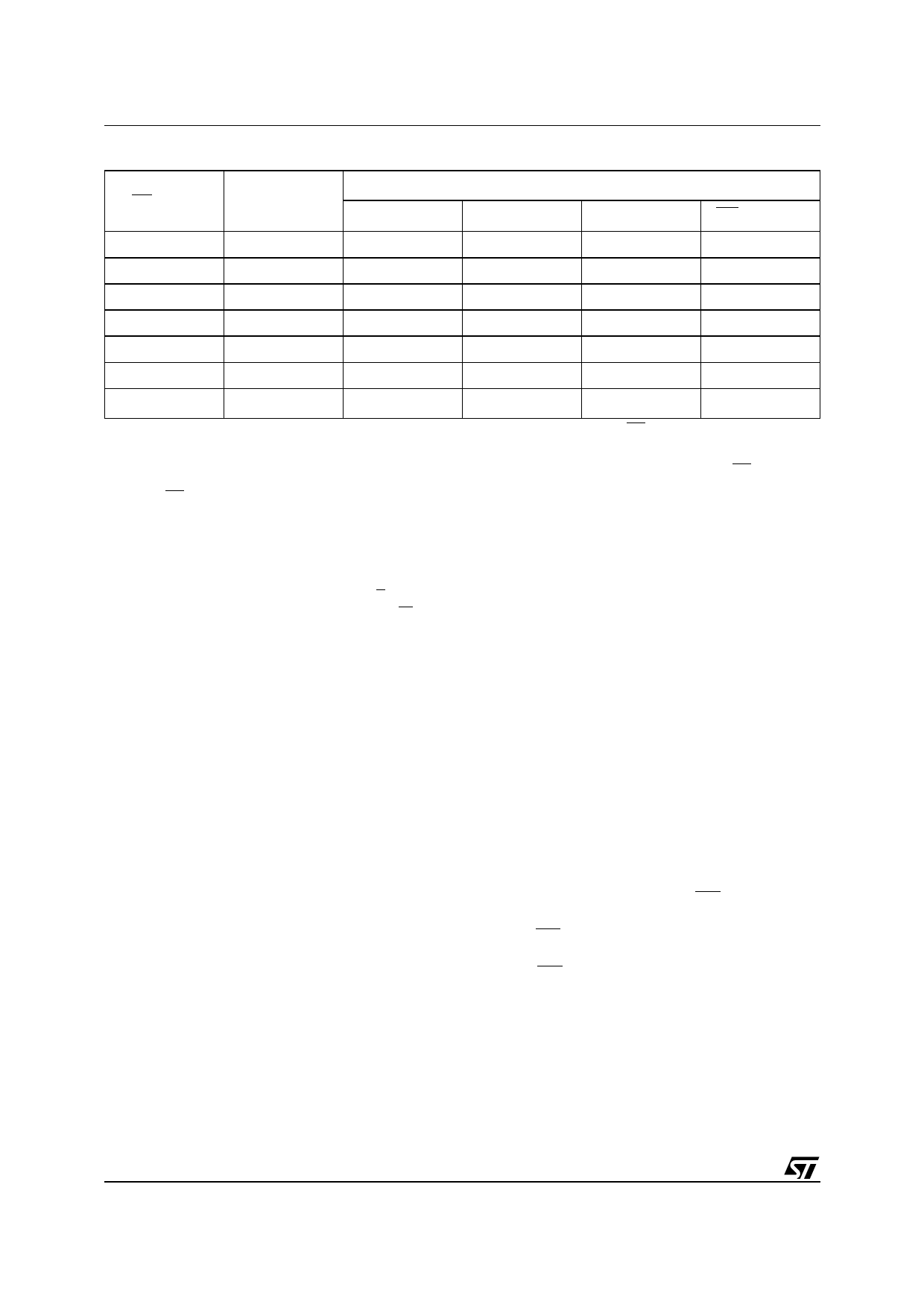

Table 16. Protection States (1)

Current State (2)

(WP, ADQ1,

ADQ0)

Program/Erase

Allowed

Protect

Next State After Event (3)

Unprotect

Lock

WP transition

100

yes

101

100

111

000

101

no

101

100

111

001

110

yes

111

110

111

011

111

no

111

110

111

011

000

yes

001

000

011

100

001

no

001

000

011

101

011

no

011

011

011

111 or 110 (4)

Note: 1. All blocks are protected at power-up, so the default configuration is 001 or 101 according to WP status.

2. Current state and Next state gives the protection status of a block. The protection status is defined by the write protect pin and by

ADQ1 (= 1 for a locked block) and ADQ0 (= 1 for a protected block) as read in the Autoselect instruction with A1 = VIH and A0 = VIL.

3. Next state is the protection status of a block after a Protect or Unprotect or Lock command has been issued or after WP has changed

its logic value.

4. A WP transition to VIH on a locked block will restore the previous ADQ0 value, giving a 111 or 110.

Program in Bypass Mode (PGBY) Instruc-

tion. This instruction uses two write cycles. The

Program command A0h is written to any Address

on the first cycle and the second write cycle latch-

es the Address on the rising edge of L and the

Data to be written on the rising edge of W and

starts the P/E.C. Read operations within the same

bank output the Status Register bits after the pro-

gramming has started. Memory programming is

made only by writing ’0’ in place of ’1’. The content

of the memory cell is not changed if the user write

’1’ in place of ’0’ and no error occurs. Status bits

ADQ6 and ADQ7 determine if programming is on-

going and ADQ5 allows verification of any possible

error.

Program (PG) Instruction. This instruction uses

four write cycles. The Program command A0h is

written to address 555h on the third cycle after two

Coded Cycles. A fourth write operation latches the

Address and the Data to be written and starts the

P/E.C. Read operations within the same bank out-

put the Status Register bits after the programming

has started. Memory programming is made only

by writing ’0’ in place of ’1’. The content of the

memory cell is not changed if the user write ’1’ in

place of ’0’ and no error occurs. Status bits ADQ6

and ADQ7 determine if programming is on-going

and ADQ5 allows verification of any possible error.

Programming at an address not in blocks being

erased is also possible during erase suspend.

Double Word Program (DPG) Instruction. This

feature is offered to improve the programming

throughput, writing a page of two adjacent words

in parallel. High voltage (11.4V to 12.6V) on VPP

pin is required. This instruction uses five write cy-

cles. The double word program command 40h is

written to address 555h on the third cycle after two

Coded Cycles. A fourth write cycle latches the ad-

dress and data to be written to the first location. A

fifth write cycle latches the new data to be written

to the second location and starts the P/E.C.. Note

that the two locations must have the same address

except for the address bit A0. The Double Word

Program can be executed in Bypass mode (DPG-

BY) to skip the two coded cycles at the beginning

of each command.

Block Protect (BP), Block Unprotect (BU),

Block Lock (BL) Instructions. All blocks are

protected and unlocked at power-up. Each block

of the array has two levels of protection against

program or erase operation. The first level is set by

the Block Protect instruction; a protected block

cannot be programmed or erased until a Block Un-

protect instruction is given for that block. A second

level of protection is set by the Block Lock instruc-

tion, and requires the use of the WP pin, according

to the following scheme:

– when WP is at VIH, the Lock status is overridden

and all blocks can be protected or unprotected;

– when WP is at VIL, Lock status is enabled; the

locked blocks are protected, regardless of their

previous protect state, and protection status

cannot be changed. Blocks that are not locked

can still change their protection status, and pro-

gram or erase accordingly;

16/49