7C1325B-100 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

7C1325B-100 Datasheet PDF : 17 Pages

| |||

CY7C1325B

I/Os must be three-stated prior to the presentation of data to

DQ[15:0] and DP[1:0]. As a safety precaution, the data lines are

three-stated once a write cycle is detected, regardless of the

state of OE.

Single Write Accesses Initiated by ADSC

This write access is initiated when the following conditions are

satisfied at clock rise: (1) CE1, CE2, and CE3 are all asserted

active, (2) ADSC is asserted LOW, (3) ADSP is deasserted

HIGH, and (4) the write input signals (GW, BWE, and BWS[1:0])

indicate a write access. ADSC is ignored if ADSP is active LOW.

The addresses presented are loaded into the address register,

burst counter/control logic and delivered to the RAM core. The

information presented to DQ[15:0] and DP[1:0] will be written

into the specified address location. Byte writes are allowed,

with BWS0 controlling DQ[7:0] and DP0 while BWS1 controlling

DQ[15:8] and DP1. All I/Os are three-stated when a write is

detected, even a byte write. Since these are common I/O de-

vices, the asynchronous OE input signal must be deasserted

and the I/Os must be three-stated prior to the presentation of

data to DQ[15:0] and DP[1:0]. As a safety precaution, the data

lines are three-stated once a write cycle is detected, regard-

less of the state of OE.

Burst Sequences

This family of devices provides a 2-bit wrap-around burst

counter inside the SRAM. The burst counter is fed by A[1:0],

and can follow either a linear or interleaved burst order. The

burst order is determined by the state of the MODE input. A

LOW on MODE will select a linear burst sequence. A HIGH on

MODE will select an interleaved burst order. Leaving MODE

unconnected will cause the device to default to an interleaved

burst sequence.

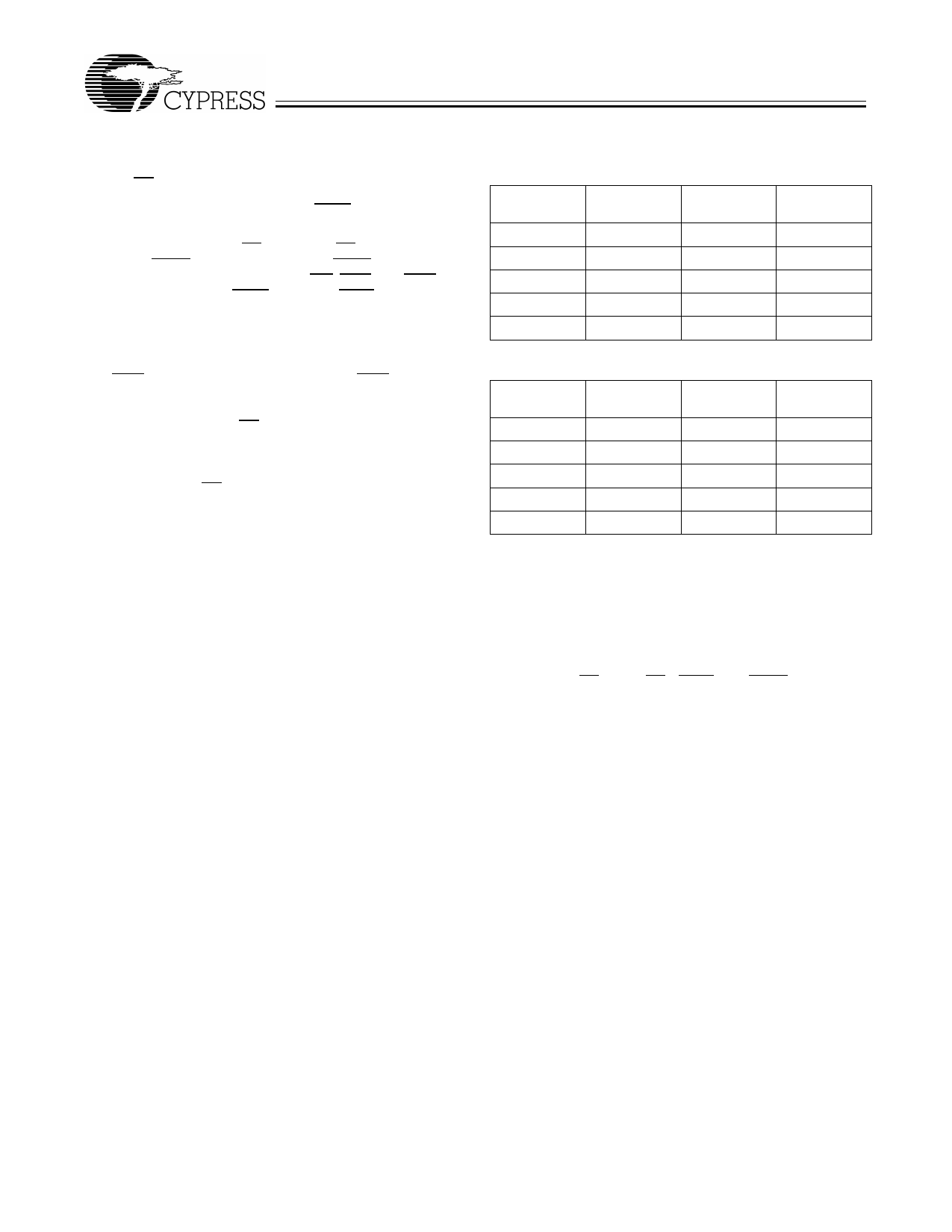

Table 1. Counter Implementation for the Intel®

Pentium®/80486 Processor’s Sequence

First

Address

AX + 1, Ax

00

01

10

11

Second

Address

AX + 1, Ax

01

00

11

10

Third

Address

AX + 1, Ax

10

11

00

01

Fourth

Address

AX + 1, Ax

11

10

01

00

Table 2. Counter Implementation for a Linear Sequence

First

Address

AX + 1, Ax

00

01

10

11

Second

Address

AX + 1, Ax

01

10

11

00

Third

Address

AX + 1, Ax

10

11

00

01

Fourth

Address

AX + 1, Ax

11

00

01

10

Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ HIGH

places the SRAM in a power conservation “sleep” mode. Two

clock cycles are required to enter into or exit from this “sleep”

mode. While in this mode, data integrity is guaranteed. Ac-

cesses pending when entering the “sleep” mode are not con-

sidered valid nor is the completion of the operation guaran-

teed. The device must be deselected prior to entering the

“sleep” mode. CE1, CE2, CE3, ADSP, and ADSC must remain

inactive for the duration of tZZREC after the ZZ input returns

LOW.

5