AD5532(2000) データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD5532 Datasheet PDF : 16 Pages

| |||

AD5532 –Typical Performance Characteristics

1.0

VREFIN = 3V

0.8 VOFFS_IN = 0V

0.6 TA = 25؇C

0.4

0.2

0.0

–0.2

–0.4

–0.6

–0.8

–1.0

0

2k 4k

6k 8k 10k 12k 14k 16k

DAC CODE

Figure 8. Typical DNL Plot

1.0

0.2

0.5

DNL MAX

0.1

INL MAX

0.0

0.0

INL MIN

–0.5

DNL MIN

–0.1

–1.0

–40

–0.2

0

40

80

TEMPERATURE – ؇C

Figure 9. INL Error and DNL Error

vs. Temperature

5.325

5.315

DAC LOADED TO MIDSCALE

VREFIN = 3V

VOFFS_IN = 0V

5.305

5.295

5.285

5.275

–40

0

40

80

TEMPERATURE – ؇C

Figure 10. VOUT vs. Temperature

3.535

TA = 25؇C

VREFIN = 3V

3.530

3.525

3.520

6

4

2

0 –2 –4 –6

SINK/SOURCE CURRENT – mA

Figure 11. VOUT Source and Sink

Capability

10.0

8.0

TA = 25؇C

VREFIN = 3V

VOFFS_IN = 0.5V

6.0

4.0

2.0

0.0

–2.0

TIME BASE – 2s/DIV

Figure 12. Full-Scale Settling Time

5.309

5.308

5.307

5.306

5.305

5.304

5.303

5.302

TA = 25؇C

VREFIN = 3V

VOFFS_IN = 0V

5.301

TIME BASE – 50ns/DIV

Figure 13. Major Code Transition

Glitch Impulse

0.0024

0.0020

0.0016

0.0012

TA = 25؇C

VREFIN = 3V

VOFFS_IN = 0V

0.0008

0.0004

0.0000

–0.0004

–0.0008

–0.0012

–0.0016

–0.0020

–0.0024

0.1

VIN – V

2.96

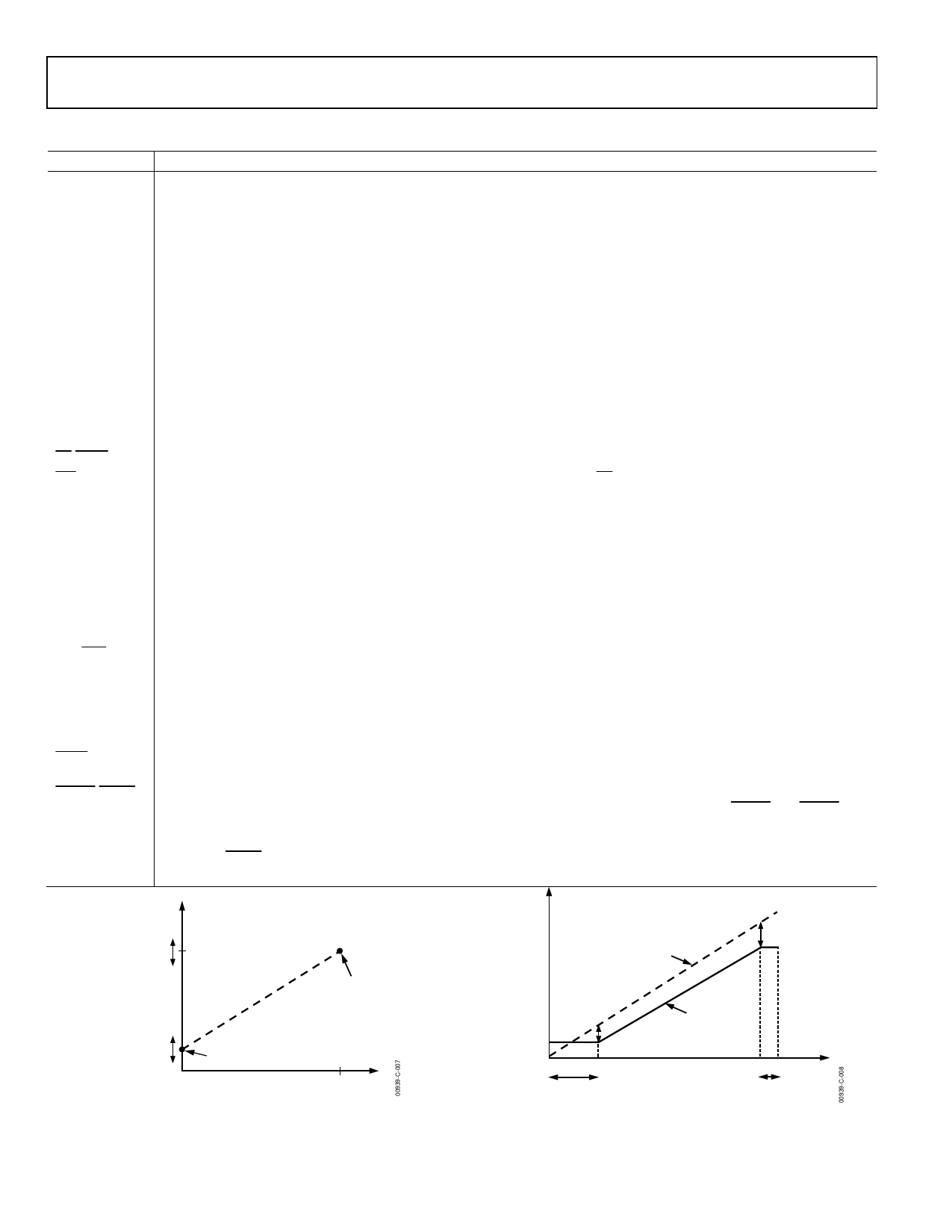

Figure 14. VIN to VOUT Accuracy

After Offset and Gain Adjustment

(SHA Mode)

5V

100

90

VOUT

10

0%

1V

BUSY

TA = 25؇C

VREFIN = 3V

VIN = 0 1.5V

2s

Figure 15. Acquisition Time and

Output Settling Time (SHA Mode)

70k

63791 TA = 25؇C

60k

VREFIN = 3V

VIN = 1.5V

50k

VOFFS_IN = 0V

40k

30k

20k

10k

200

0

5.2670

5.2676

VOUT – V

1545

5.2682

Figure 16. SHA-Mode Repeatability

(64K Acquisitions)

–10–

REV. 0