LH28F320SKTD-L70 гғҮгғјгӮҝгӮ·гғјгғҲгҒ®иЎЁзӨәпјҲPDFпјү - Sharp Electronics

йғЁе“Ғз•ӘеҸ·

гӮігғігғқгғјгғҚгғігғҲиӘ¬жҳҺ

гғЎгғјгӮ«гғј

LH28F320SKTD-L70 Datasheet PDF : 66 Pages

| |||

sharp

LHF32KZ5

3

1 INTRODUCTION

This datasheet contains LH28F320SKTD-L70

specifications. Section 1 provides a flash memory

overview. Sections 2, 3, 4, and 5 describe the

memory organization and functionality. Section 6

covers electrical specifications.

1.1 Product Overview

The LH28F320SKTD-L70 is a high-performance 32-

Mbit Smart3/5 Dual Work Flash memory organized

as 2MBx8/1MBx16 x 2Bnak. The 4MB of data is

arranged in sixty-four 64-Kbyte blocks which are

individually erasable, lockable, and unlockable in-

system. The memory map is shown in Figure 3.

Smart3/5 technology provides a choice of VCC and

VPP combinations, as shown in Table 1, to meet

system performance and power expectations. 2.7V

VCC consumes approximately one-fifth the power of

5V VCC. But, 5V VCC provides the highest read

performance. VPP at 2.7V, 3.3V and 5V eliminates

the need for a separate 12V converter, while VPP=5V

maximizes erase and write performance. In addition

to flexible erase and program voltages, the dedicated

VPP pin gives complete data protection when VPP вүӨ

VPPLK.

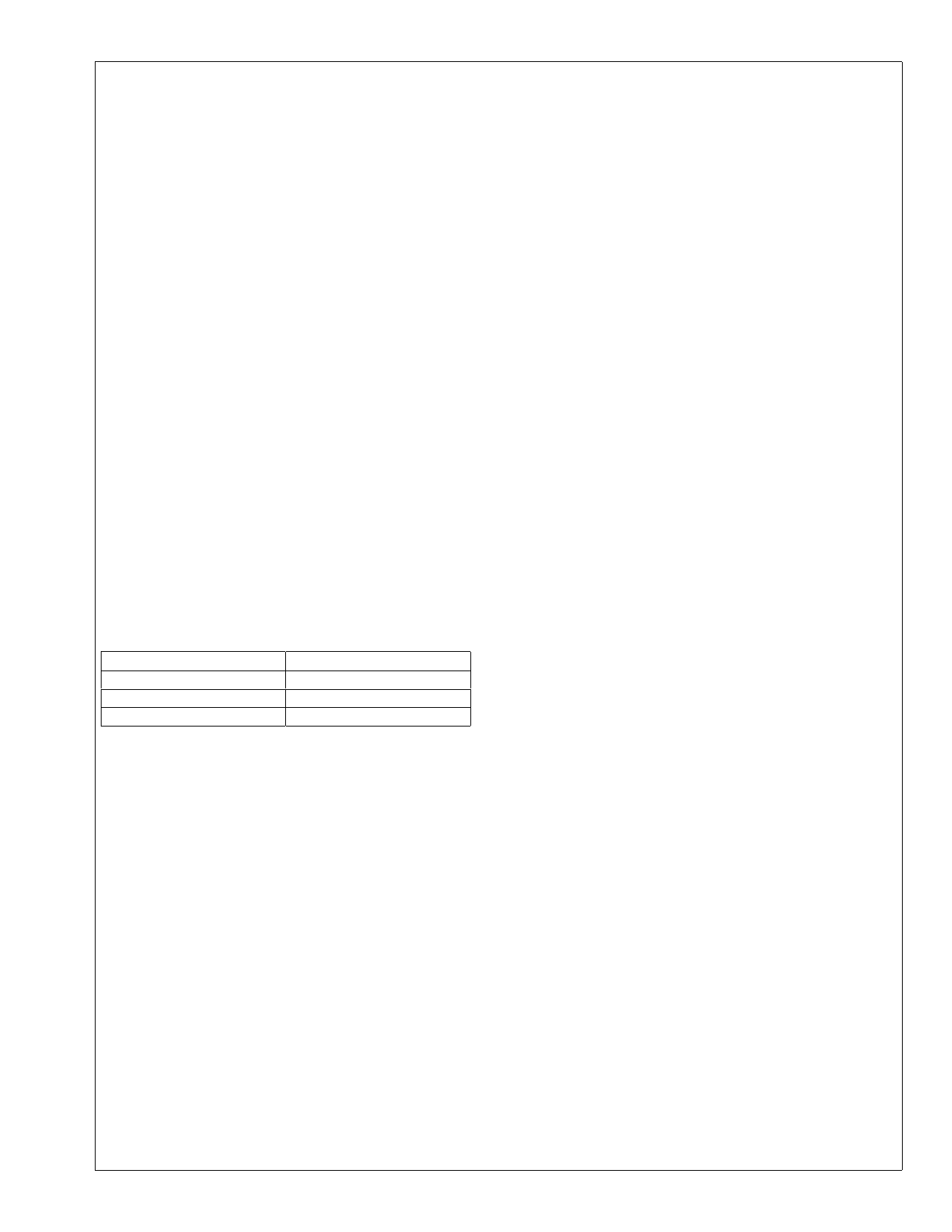

Table 1. VCC and VPP Voltage Combinations

Offered by Smart3/5 Technology

VCC Voltage

2.7V

VPP Voltage

2.7V, 3.3V, 5V

3.3V

3.3V, 5V

5V

5V

Internal VCC and VPP detection Circuitry

automatically configures the device for optimized

read and write operations.

A Command User Interface (CUI) serves as the

interface between the system processor and internal

operation of the device. A valid command sequence

written to the CUI initiates device automation. An

internal Write State Machine (WSM) automatically

executes the algorithms and timings necessary for

block erase, bank erase, (multi) word/byte write and

block lock-bit configuration operations.

A block erase operation erases one of the deviceвҖҷs

64-Kbyte blocks typically within 0.34s (5V VCC, 5V

VPP) independent of other blocks. Each block can be

independently erased 100,000 times (3.2 million

block erases per bank). Block erase suspend mode

allows system software to suspend block erase to

read or write data from any other block.

A word/byte write is performed in byte increments

typically within 9.24Вөs (5V VCC, 5V VPP). A multi

word/byte write has high speed write performance of

2Вөs/byte (5V VCC, 5V VPP). (Multi) Word/byte write

suspend mode enables the system to read data or

execute code from any other flash memory array

location.

Individual block locking uses a combination of bits

and WP#, Sixty-four block lock-bits, to lock and

unlock blocks. Block lock-bits gate block erase, bank

erase and (multi) word/byte write operations. Block

lock-bit configuration operations (Set Block Lock-Bit

and Clear Block Lock-Bits commands) set and

cleared block lock-bits.

The status register indicates when the WSMвҖҷs block

erase, bank erase, (multi) word/byte write or block

lock-bit configuration operation is finished.

The STS output gives an additional indicator of WSM

activity by providing both a hardware signal of status

(versus software polling) and status masking

(interrupt masking for background block erase, for

example). Status polling using STS minimizes both

CPU overhead and system power consumption. STS

pin can be configured to different states using the

Configuration command. The STS pin defaults to

RY/BY# operation. When low, STS indicates that the

WSM is performing a block erase, bank erase, (multi)

word/byte write or block lock-bit configuration. STS-

High Z indicates that the WSM is ready for a new

command, block erase is suspended and (multi)

word/byte write are inactive, (multi) word/byte write

are suspended, or the device is in deep power-down

mode. The other 3 alternate configurations are all

pulse mode for use as a system interrupt.