CYRF69213 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CYRF69213 Datasheet PDF : 86 Pages

| |||

CYRF69213

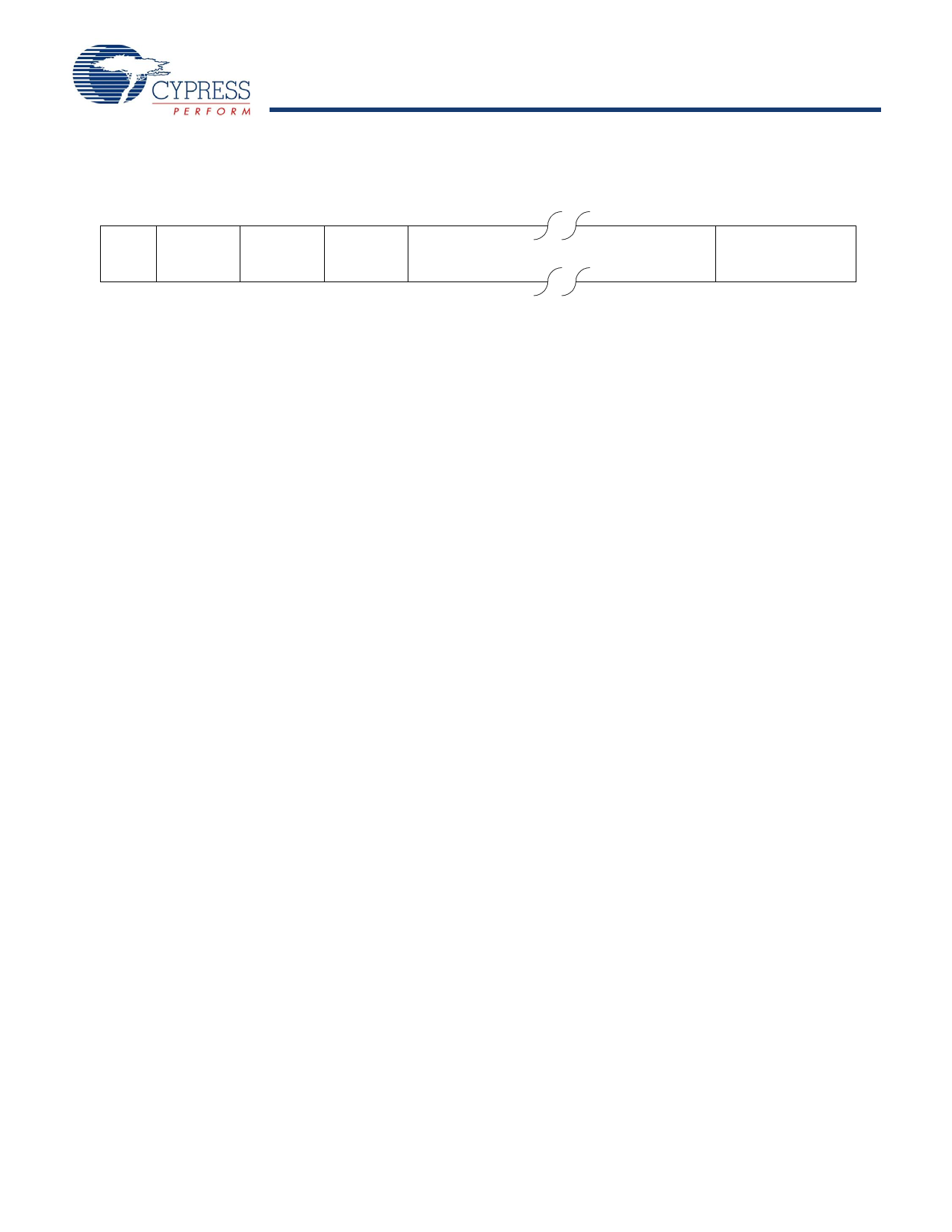

Preamble

n x 16us

2nd Framing

Symbol*

Figure 2. Example Default Packet Format

P

SOP 1 SOP 2 Length Payload Data

CRC 16

1st Framing

Symbol*

Packet

length

1 Byte

Period

Packet Buffers

Packet data and configuration registers are accessed through

the SPI interface. All configuration registers are directly

addressed through the address field in the SPI packet.

Configuration registers are provided to allow configuration of

DSSS PN codes, data rate, operating mode, interrupt masks,

interrupt status, and others.

Packet Buffers

All data transmission and reception uses the 16-byte packet

buffers—one for transmission and one for reception.

The transmit buffer allows a complete packet of up to 16 bytes of

payload data to be loaded in one burst SPI transaction.This is

then transmitted with no further MCU intervention. Similarly, the

receive buffer allows an entire packet of payload data up to 16

bytes to be received with no firmware intervention required until

packet reception is complete.

The CYRF69213 IC supports packet length of up to 40 bytes;

interrupts are provided to allow an MCU to use the transmit and

receive buffers as FIFOs. When transmitting a packet longer

than 16 bytes, the MCU can load 16 bytes initially, and add

further bytes to the transmit buffer as transmission of data

creates space in the buffer. Similarly, when receiving packets

longer than 16 bytes, the MCU function must fetch received data

from the FIFO periodically during packet reception to prevent it

from overflowing.

Auto Transaction Sequencer (ATS)

The CYRF69213 IC provides automated support for

transmission and reception of acknowledged data packets.

When transmitting a data packet, the device automatically starts

the crystal and synthesizer, enters transmit mode, transmits the

packet in the transmit buffer, and then automatically switches to

receive mode and waits for a handshake packet — and then

automatically reverts to sleep mode or idle mode when either an

ACK packet is received, or a timeout period expires.

Similarly, when receiving in transaction mode, the device waits

in receive mode for a valid packet to be received, then

automatically transitions to transmit mode, transmits an ACK

packet, and then switches back to receive mode to await the next

packet. The contents of the packet buffers are not affected by the

transmission or reception of ACK packets.

In each case, the entire packet transaction takes place without

any need for MCU firmware action; to transmit data the MCU

simply needs to load the data packet to be transmitted, set the

length, and set the TX GO bit. Similarly, when receiving packets

*Note:32 or 64us

in transaction mode, firmware simply needs to retrieve the fully

received packet in response to an interrupt request indicating

reception of a packet.

Interrupts

The radio function provides an interrupt (IRQ) output, which is

configurable to indicate the occurrence of various different

events. The IRQ pin may be programmed to be either active high

or active low, and be either a CMOS or open drain output. The

IRQ pin can be multiplexed on the SPI if routed to an external pin.

The radio function features three sets of interrupts: transmit,

receive, and system interrupts. These interrupts all share a

single pin (IRQ), but can be independently enabled/disabled. In

transmit mode, all receive interrupts are automatically disabled,

and in receive mode all transmit interrupts are automatically

disabled. However, the contents of the enable registers are

preserved when switching between transmit and receive modes.

If more than one radio interrupt is enabled at any time, it is

necessary to read the relevant status register to determine which

event caused the IRQ pin to assert. Even when a given interrupt

source is disabled, the status of the condition that would

otherwise cause an interrupt can be determined by reading the

appropriate status register. It is therefore possible to use the

devices without making use of the IRQ pin by polling the status

register(s) to wait for an event, rather than using the IRQ pin.

The microcontroller function supports 23 maskable interrupts in

the vectored interrupt controller. Interrupt sources include a USB

bus reset, LVR/POR, a programmable interval timer, a 1.024-ms

output from the Free Running Timer, three USB endpoints, two

capture timers, five GPIO Ports, three GPIO pins, two SPI, a

16-bit free running timer wrap, an internal wakeup timer, and a

bus active interrupt. The wakeup timer causes periodic interrupts

when enabled. The USB endpoints interrupt after a USB

transaction complete is on the bus. The capture timers interrupt

whenever a new timer value is saved due to a selected GPIO

edge event. A total of eight GPIO interrupts support both TTL or

CMOS thresholds. For additional flexibility, on the edge sensitive

GPIO pins, the interrupt polarity is programmable to be either

rising or falling.

Clocks

The radio function has a 12 MHz crystal (30-ppm or better)

directly connected between XTAL and GND without the need for

external capacitors. A digital clock out function is provided, with

selectable output frequencies of 0.75, 1.5, 3, 6, or 12 MHz. This

output may be used to clock an external microcontroller (MCU)

or ASIC. This output is enabled by default, but may be disabled.

Document Number: 001-07552 Rev. *H

Page 10 of 86