D950CORE データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

D950CORE Datasheet PDF : 89 Pages

| |||

D950-Core

Data buses (XD/YD and XA/YA) are provided externally. Data memories (RAM, ROM) and

peripherals registers are to be mapped in these address spaces.

Instruction bus (ID/IA) gives access to program memory (RAM, ROM). Each bus has its own

control interface

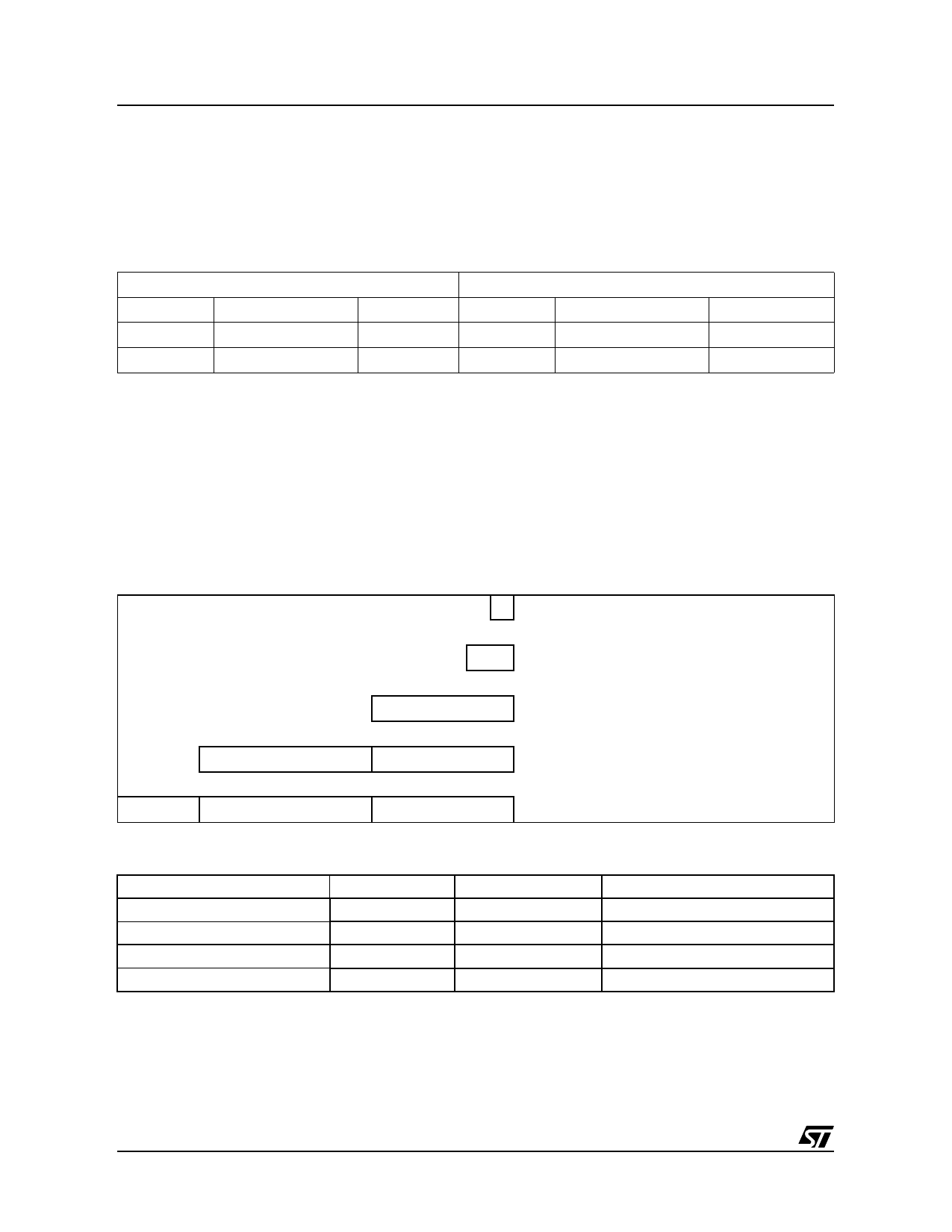

Table 3.1 Data/Instruction Bus and Corresponding Address Bus.

Data / Instruction Buses

XD

Bidirectional

16-bit

YD

Bidirectional

16-bit

ID

Bidirectional

16-bit

Corresponding Address Bus

XA

Unidirectional

16-bit

YA

Unidirectional

16-bit

IA

Unidirectional

16-bit

Depending on the calculation mode, the D950-Core DCU computes operands which can be

considered as 16 or 32-bit, signed or unsigned. It includes a 16 x 16-bit parallel multiplier able

to implement MAC-based functions in one cycle per MAC. A 40-bit arithmetic and logic unit,

including a 8-bit extension for arithmetic operations, implements a wide range of arithmetic

and logic functions. A 40-bit barrel shifter unit and a bit manipulation unit are included.

Tables 3.2 and 3.3 illustrate the different types of word length and word format available for

manipulation.

Table 3.2

Summary of Possible Word Lengths

0

1-bit word

70

8-bit word

15

0

16-bit word signed / unsigned

31

16 15

0

32-bit word signed / unsigned

39 32

31

16 15

0

40-bit word signed / unsigned

Table 3.3 Summary of Possible Word Formats

Format

fractional

integer

signed

unsigned

signed

unsigned

Minimum

-1

0

- 32768

0

Maximum

+ 0.999969481

+ 0.99996948

+ 32767

+ 65535

12/89