QL3004 データシートの表示(PDF) - QuickLogic Corporation

部品番号

コンポーネント説明

メーカー

QL3004

QL3004 Datasheet PDF : 49 Pages

| |||

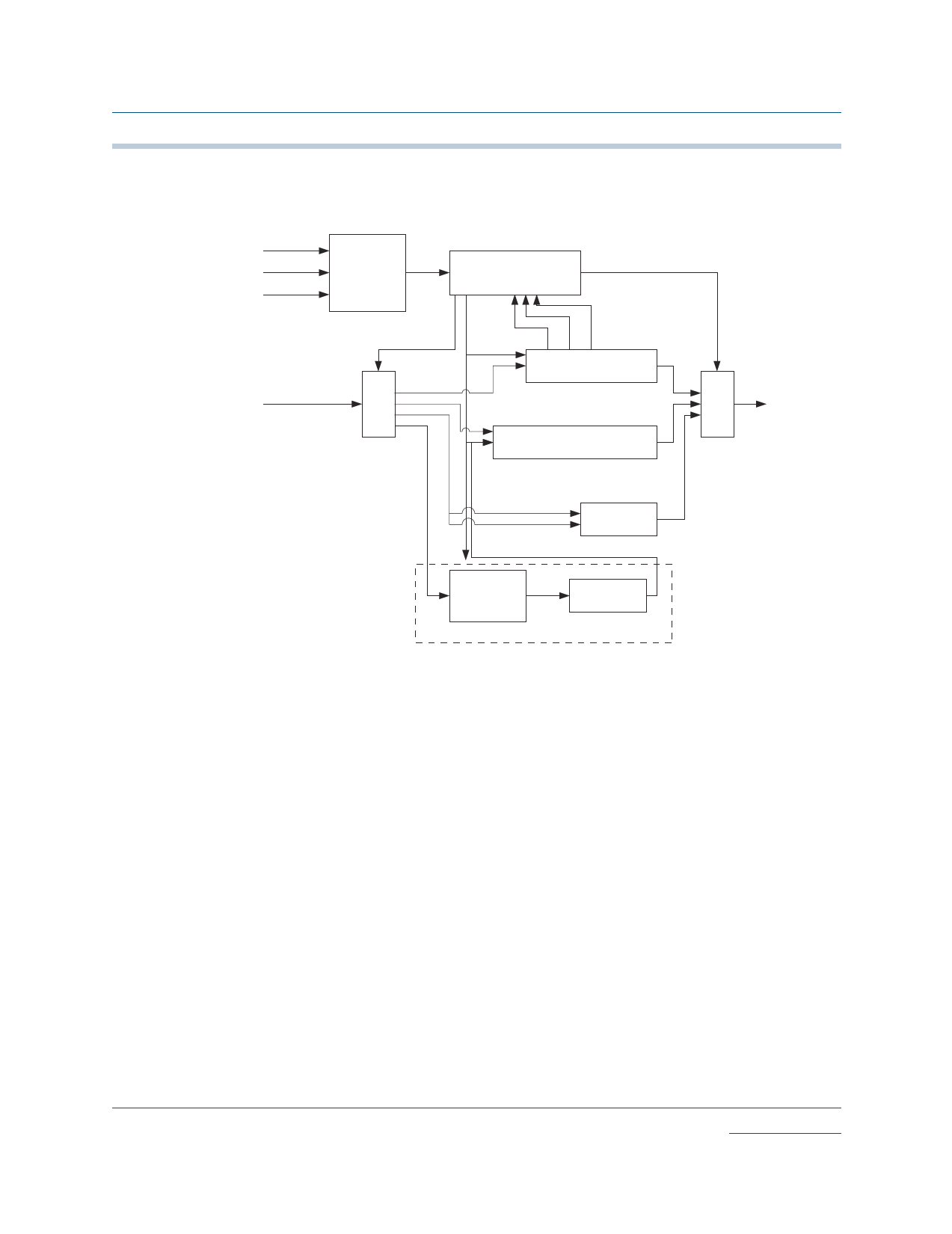

JTAG

TCK

TMS

TRSTB

pASIC 3 FPGA Family Data Sheet Rev. D

Figure 6: JTAG Block Diagram

TAp Controller

State Machine

(16 States)

Instruction Decode

&

Control Logic

RDI

Mux

Instruction Register

Boundary-Scan Register

(Data Register)

Mux

TDO

Bypass

Register

Internal

Register

I/O Registers

User Defined Data Register

Microprocessors and Application Specific Integrated Circuits (ASICs) pose many design challenges, not the

least of which concerns the accessibility of test points. The Joint Test Access Group (JTAG) formed in response

to this challenge, resulting in IEEE standard 1149.1, the Standard Test Access Port and Boundary Scan

Architecture.

The JTAG boundary scan test methodology allows complete observation and control of the boundary pins of

a JTAG-compatible device through JTAG software. A Test Access Port (TAP) controller works in concert with

the Instruction Register (IR); these allow users to run three required tests, along with several user-defined tests.

JTAG tests allow users to reduce system debug time, reuse test platforms and tools, and reuse subsystem tests

for fuller verification of higher level system elements.

The 1149.1 standard requires the following three tests:

• Extest Instruction. The Extest Instruction performs a printed circuit board (PCB) interconnect test. This

test places a device into an external boundary test mode, selecting the boundary scan register to be

connected between the TAP Test Data In (TDI) and Test Data Out (TDO) pins. Boundary scan cells are

preloaded with test patterns (via the Sample/Preload Instruction), and input boundary cells capture the input

data for analysis.

• Sample/Preload Instruction. The Sample/Preload Instruction allows a device to remain in its functional

mode, while selecting the boundary scan register to be connected between the TDI and TDO pins. For this

test, the boundary scan register can be accessed via a data scan operation, allowing users to sample the

functional data entering and leaving the device.

© 2005 QuickLogic Corporation

www.quicklogic.com

•

•••

••

9