FM24CL64-S データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

メーカー

FM24CL64-S Datasheet PDF : 13 Pages

| |||

that are loaded into the internal address latch. After

the FM24CL64 acknowledges the address, the bus

master issues a start condition. This simultaneously

aborts the write operation and allows the read

FM24CL64

command to be issued with the device address LSB

set to a 1. The operation is now a current address

read.

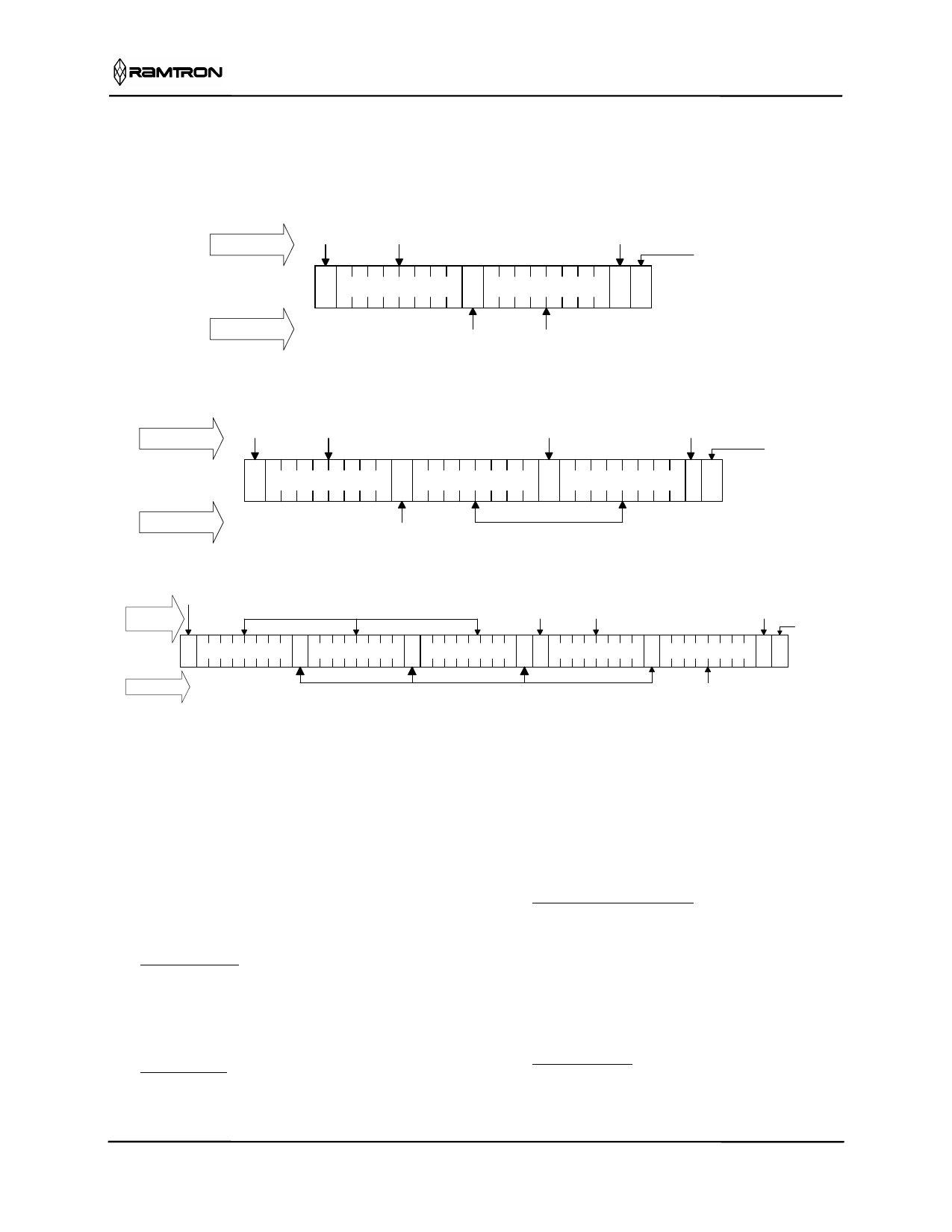

By Master

Start

Address

S

Slave Address 1 A

No

Acknowledge

Data Byte

1P

Stop

By FM24CL64

Acknowledge Data

Figure 7. Current Address Read

By Master

Start

Address

Acknowledge

No

Acknowledge

S

Slave Address 1 A

Data Byte

A

Data Byte

1P

Stop

By FM24CL64

Acknowledge

Data

Figure 8. Sequential Read

Start

By Master

Address

Start

Address

S

Slave Address 0 A

Address MSB

A

Address LSB

AS

Slave Address 1 A

By FM24CL64

Acknowledge

No

Acknowledge

Stop

Data Byte

1P

Data

Figure 9. Selective (Random) Read

Applications

Clearly the strength of higher write endurance and

faster writes make FRAM superior to EEPROM in all

but one-time programmable applications. The

advantage is most obvious in data collection

environments where writes are frequent and data

must be nonvolatile, but the benefits combine in other

ways. A short list of ideas is provided here.

1. Data collection. In applications where data is

collected and saved, FRAM provides a superior

alternative to other solutions. It is more cost effective

than battery backup for SRAM and provides better

write attributes than EEPROM.

2. Configuration. Any nonvolatile memory can

retain a configuration. However, if the configuration

changes and power failure is a possibility, the higher

Rev 2.0

July 2003

write endurance of FRAM allows changes to be

recorded without restriction. Any time the system

state is altered, the change can be written. This avoids

writing to memory on power down when the

available time is short and power scarce.

3. High noise environments. Writing to EEPROM

in a noisy environment can be challenging. When

severe noise or power fluctuations are present, the

long write time of EEPROM creates a window of

vulnerability during which the write can be

corrupted. The fast write of FRAM is complete

within a microsecond. This time is typically too short

for noise or power fluctuation to disturb it.

4. Time to market. In a complex system, multiple

software routines may need to access the nonvolatile

memory. In this environment the time delay

associated with programming EEPROM adds undue

Page 7 of 13