FM31256 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

FM31256 Datasheet PDF : 27 Pages

| |||

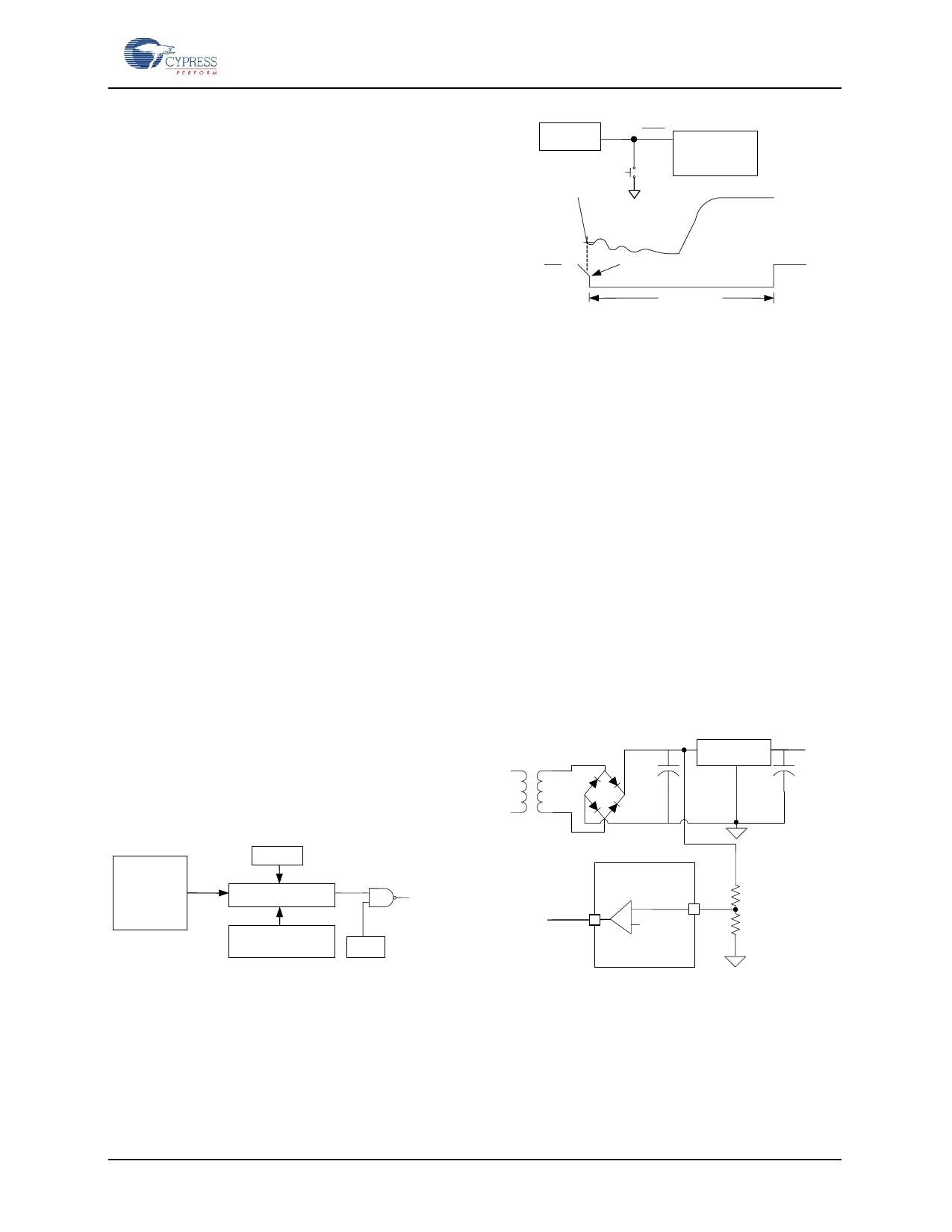

The watchdog timer can also be used to assert the

reset signal (/RST). The watchdog is a free running

programmable timer. The period can be software

programmed from 100 ms to 3 seconds in 100 ms

increments via a 5-bit nonvolatile register. All

programmed settings are minimum values and vary

with temperature according to the operating

specifications. The watchdog has two additional

controls associated with its operation, a watchdog

enable bit (WDE) and timer restart bits (WR). Both

the enable bit must be set and the watchdog must

timeout in order to drive /RST active. If a reset event

occurs, the timer will automatically restart on the

rising edge of the reset pulse. If WDE=0, the

watchdog timer runs but a watchdog fault will not

cause /RST to be asserted low. The WTR flag will be

set, indicating a watchdog fault. This setting is useful

during software development and the developer does

not want /RST to drive. Note that setting the

maximum timeout setting (11111b) disables the

counter to save power. The second control is a nibble

that restarts the timer preventing a reset. The timer

should be restarted after changing the timeout value.

The watchdog timeout value is located in register

0Ah, bits 4-0, and the watchdog enable is bit 7. The

watchdog is restarted by writing the pattern 1010b to

the lower nibble of register 09h. Writing this pattern

will also cause the timer to load new timeout values.

Writing other patterns to this address will not affect

its operation. Note the watchdog timer is free-

running. Prior to enabling it, users should restart the

timer as described above. This assures that the full

timeout period will be set immediately after enabling.

The watchdog is disabled when VDD is below VTP.

The following table summarizes the watchdog bits. A

block diagram follows.

Watchdog timeout

Watchdog enable

Watchdog restart

100 ms

clock

Timebase

WDT4-0 0Ah, bits 4-0

WDE

0Ah, bit 7

WR3-0 09h, bits 3-0

WR3-0 = 1010b to restart

Counter

/RST

Watchdog

timeout

WDE

Figure 3. Watchdog Timer

Manual Reset

The /RST pin is bi-directional and allows the

FM31xx to filter and de-bounce a manual reset

switch. The /RST input detects an external low

condition and responds by driving the /RST signal

low for 100 ms.

Document Number: 001-86391 Rev. *B

FM31256/3164 Processor Companion

MCU

RST

Reset

Switch

FM31xx

Switch

Behavior

FM31xx

RST

drives

100 ms (min.)

Figure 4. Manual Reset

Note that an internal weak pull-up on /RST

eliminates the need for additional external

components.

Reset Flags

In case of a reset condition, a flag will be set to

indicate the source of the reset. A low VDD reset is

indicated by the POR flag, register 09h bit 6. A

watchdog reset is indicated by the WTR flag, register

09h bit 7. Note that the flags are internally set in

response to reset sources, but they must be cleared by

the user. When the register is read, it is possible that

both flags are set if both have occurred since the user

last cleared them.

Early Power Fail Comparator

An early power fail warning can be provided to the

processor well before VDD drops out of spec. The

comparator is used to create a power fail interrupt

(NMI). This can be accomplished by connecting the

PFI pin to the unregulated power supply via a resistor

divider. An application circuit is shown below.

Regulator

VDD

FM31xx

To MCU CAL/PFO

NMI input

PFI

+

- 1.2V ref

Figure 5. Comparator as Early Power-Fail Warning

The voltage on the PFI input pin is compared to an

onboard 1.2V reference. When the PFI input voltage

drops below this threshold, the comparator will drive

the CAL/PFO pin to a low state. The comparator has

100 mV (max) of hysteresis to reduce noise

sensitivity, only for a rising PFI signal. For a falling

PFI edge, there is no hysteresis.

Page 5 of 27