SK100E445(2001) データシートの表示(PDF) - Semtech Corporation

部品番号

コンポーネント説明

メーカー

SK100E445 Datasheet PDF : 8 Pages

| |||

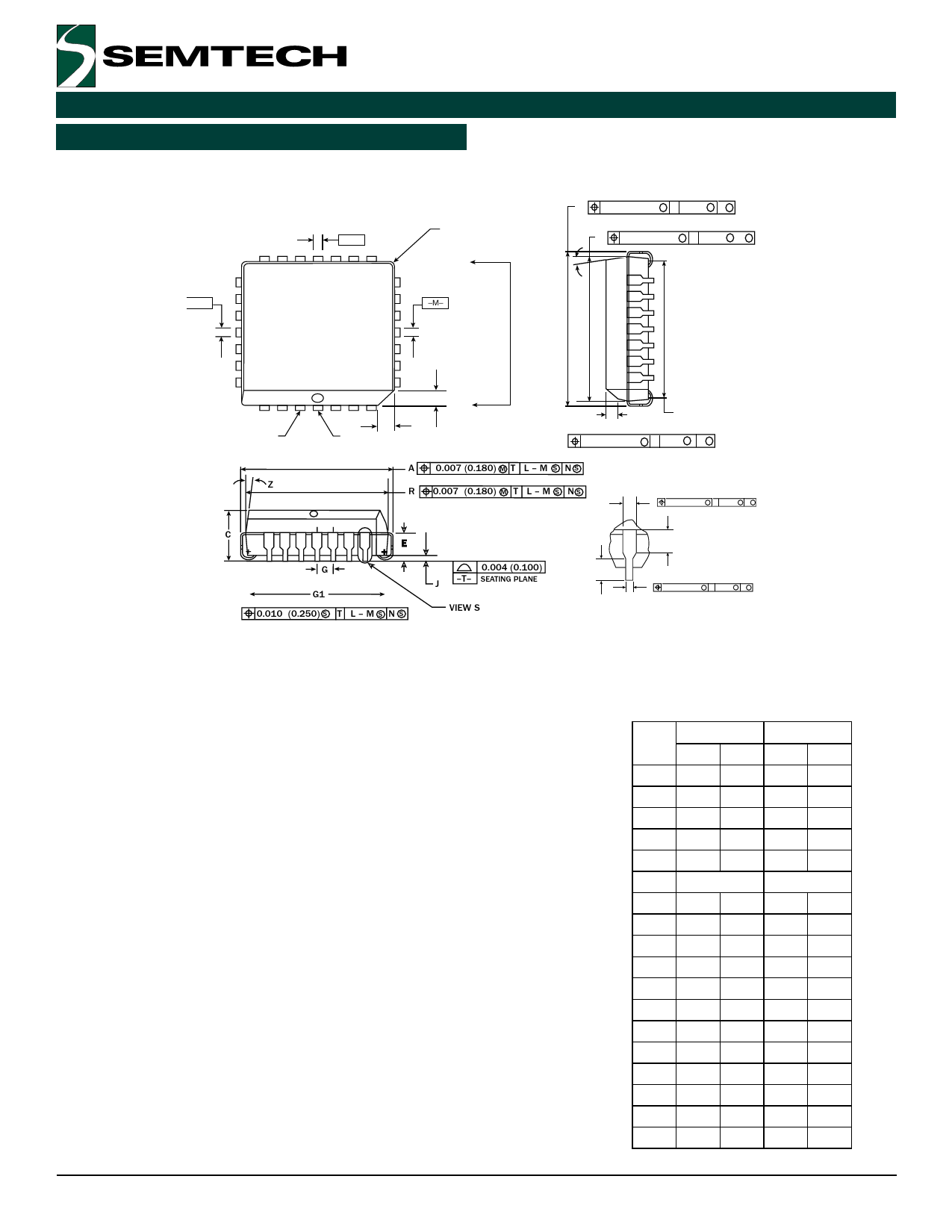

SK10/100E445

HIGH-PER.ORMANCE PRODUCTS

Application Information

The SK10/100E445 is an integrated 4-bit serial-to-

parallel data converter. The chip is designed to work

with the E446 device to provide both transmission and

receiving of a high speed serial data path. The E445

can convert up to a 2.0 GB/s NRZ data stream into 4-bit

parallel data. The device also provides a divide by four

clock output to be used to synchronize the parallel data

with the rest of the system.

The E445 features multiplexed dual serial inputs to

provide test loop capability when used in conjunction

with the E446. Figure 1 illustrates the loop test

architecture. The architecture allows for the electrical

testing of the link without requiring actual transmission

over the serial data path medium. The SINA serial input

of the E446 has an extra buffer delay and should be

used as the loopback serial input.

The clock frequency is significantly lower than that of

a single converter. To increase this frequency, some

games can be played with the clock input of the higher

order E445. By delaying the clock feeding the second

E445 relative to the clock of the first E445, the

frequency of operation can be increased. The delay

between the two clocks can be increased until the

minimum delay of clock to serial out would potentially

cause a serial bit to be swallowed (Figure 3).

CLOCK

CLOCK*

E445a

E445b

SERIAL

INPUT

DATA

SIN

SIN*

SOUT

SOUT*

Q3 Q2 Q1 Q0

SIN

SIN*

Q3 Q2 Q1 Q0

Q7 Q6 Q5 Q4

Q3 Q2 Q1 Q0

PARALLEL

DATA

SOUT

SOUT*

TO SERIAL

MEDIUM

PARALLEL OUTPUT DATA

PARALLEL

DATA

SINA

SINA*

FROM SERIAL

MEDIUM

Figure 1. Loopback Test Architecture

CLOCK

Tpd CLK

to SOUT

800 ps

1150 ps

100 ps

Figure 2. Cascaded 1:8 Converter Architecture

The E445 features a differential serial output and a divide

by 8 clock output to facilitate the cascading of two devices

to build a 1:8 demultiplexer. Figure 2 illustrates the

architecture for a 1:8 demultiplexer using two E445’s;

the timing diagram for this configuration can be found in

Figure 6. Notice the serial outputs (SOUT of the lower

order converter feed the serial inputs of the higher order

device. This feedthrough of the serial inputs bounds

the upper end of the frequency of operation. The clock

to serial output propagation delay plus the setup time of

the serial input pins must fit into a single clock period

for the cascade architecture to function properly. Using

the worst case values for these two parameters from

the datasheet, TPD CLK to SOUT = 1150 ps and tS for

SIN = –100 ps, yields a minimum period of 1050 ps or a

clock frequency of 950 MHz.

With a minimum delay of 800 ps on this output, the

clock for the lower order E445 cannot be delayed more

than 800 ps relative to the clock of the first E445 with-

out potentially missing a bit of information. Because

the setup time on the serial input pin is negative, coinci-

dent excursions on the data and clock inputs of the E445

will result in correct operation.

CLOCK A

CLOCK B

Tpd CLK

to SOUT

800 ps

1150 ps

Figure 3. Cascade Frequency Limitation

Revision 1/.ebruary 21, 2001

3

www.semtech.com