SK100E445PJ データシートの表示(PDF) - Semtech Corporation

部品番号

コンポーネント説明

メーカー

SK100E445PJ Datasheet PDF : 9 Pages

| |||

HIGH-PER.ORMANCE PRODUCTS

Description

SK10/100E445

4-Bit Serial/Parallel Converter

.eatures

The SK10/100E445 is an integrated 4-bit serial-to-

parallel data converter. The device is designed to

operate for NRZ data rates of up to 2.0 Gb/s. The

chip generates a divide by 4 and a divide by 8 clock

for both 4-bit conversion and a two chip 8-bit conversion

function. The conversion sequence was chosen to

convert the first serial bit to Q0, the second to Q1,

etc.

The start bit for conversion can be moved using the SYNC

input. A single pulse applied asynchronously for at least

two input clock cycles shifts the start bit for conversion

from Qn to Qn–1. For each additional shift required, an

additional pulse must be applied to the SYNC input.

Asserting the SYNC input will force the internal clock

dividers to “swallow” a clock pulse, effectively shifting a

bit from the Qn to the Qn–1 output (see Timing Diagram

B).

The MODE input is used to select the conversion mode

of the device. With the MODE input LOW, or open, the

device will function as a 4-bit converter. When the

MODE input is driven HIGH, the data on the output will

change on every eighth clock cycle, thus allowing for

an 8-bit conversion scheme using two E445’s. When

cascaded in an 8-bit conversion scheme, the devices

will not operate at the 2.0 Gb/s data rate of a single

device. Refer to the applications section of this data

sheet for more information on cascading the E445.

• Extended 100E VEE Range of –4.2V to –5.5V

• On-Chip Clock ÷ 4 and ÷8

• 2.0 Gb/s Data Rate Capability

• Differential Clock and Serial Inputs

• VBB Output for Single-Ended Input Applications

• Asynchronous Data Synchronization

• Mode Select to Expand to 8-Bits

• Internal 75KΩ Input Pulldown Resistors

• ESD Protection of >4000V

• Fully Compatible with MC10/100E445

• Available in 28-Pin PLCC Package

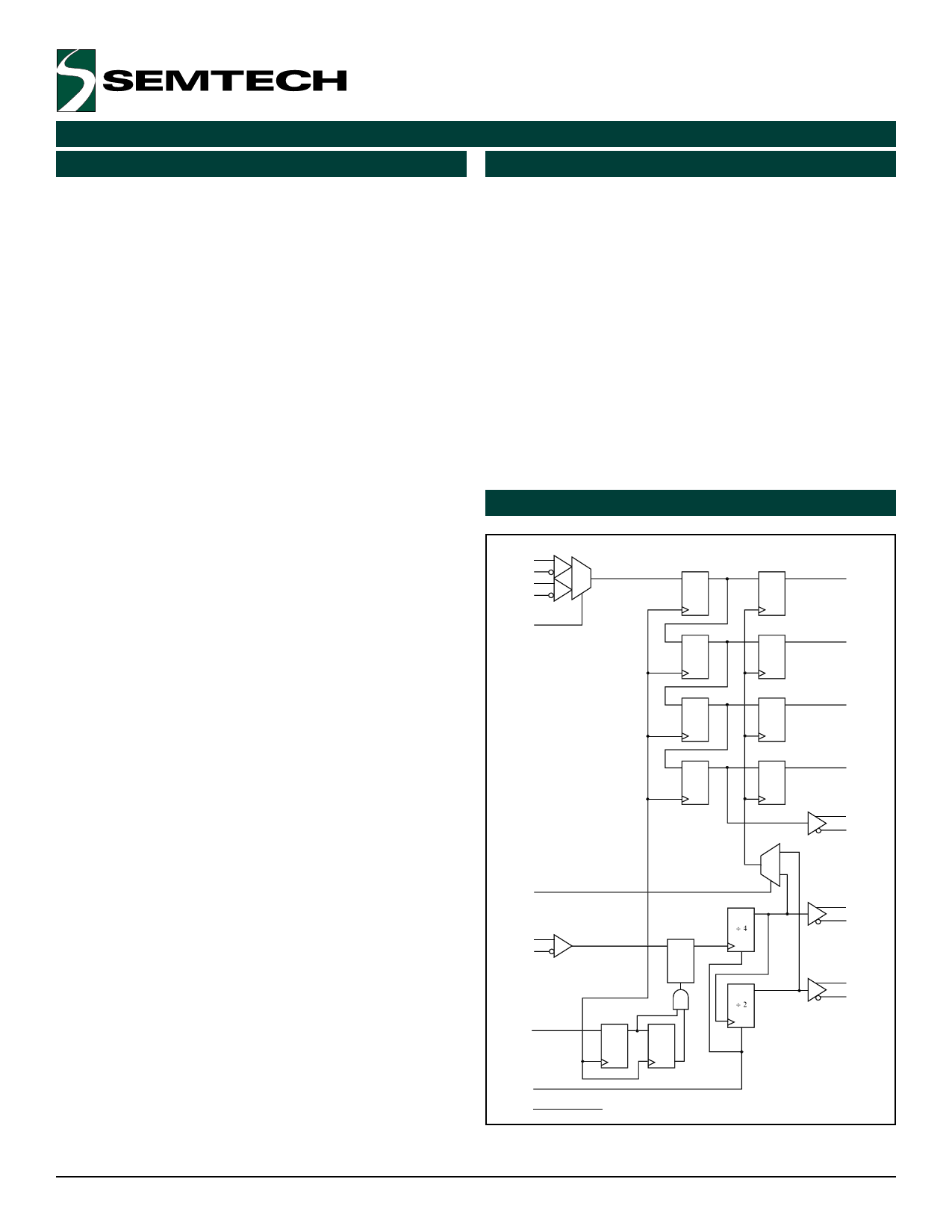

.unctional Block Diagram

SINB

SINB*

SINA

SINA*

SEL

DQ

DQ

Q3

DQ

DQ

Q2

DQ

DQ

Q1

DQ

DQ

Q0

SOUT

For lower data rate applications, a VBB reference voltage

SOUT*

is supplied for single-ended inputs. When operating at

0

clock rates above 500 MHz, differential input signals

1

are recommended. For single-ended inputs, the VBB pin

MODE

is tied to the inverting differential input and bypassed

via a 0.01 µF capacitor. The VBB provides the switching

CLK

reference for the input differential amplifier. The VBB

CLK*

In Out

Latch

Out

¸4

R

CL/4

CL/4*

can also be used to AC couple an input signal.

Upon power-up, the internal flip-flops will attain a random

EN

Out

¸2

CL/8

CL/8*

R

state. To synchronize multiple E445’s in a system, the SYNC

DQ

D

master reset must be asserted.

Q*

RESET

VBB

Revision 2/April 10, 2002

1

www.semtech.com