992215735011 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

メーカー

992215735011 Datasheet PDF : 17 Pages

| |||

Philips Semiconductors

Frame Transfer CCD Image Sensor

Product specification

FTT1010-M

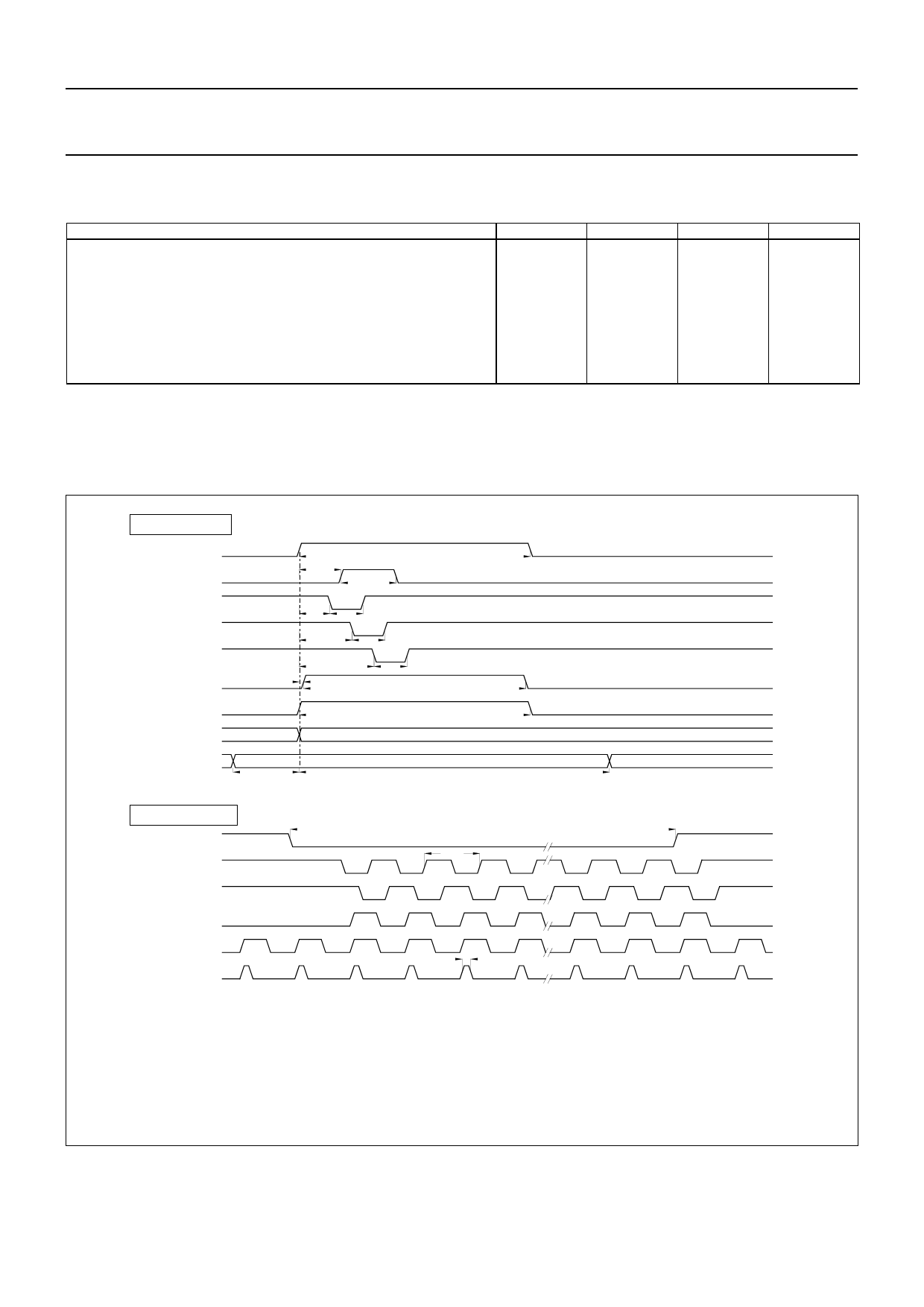

Timing diagrams (for default operation)

AC CHARACTERISTICS

Horizontal frequency (1/Tp) 1

Vertical frequency

Charge Reset (CR) time

Rise and fall times: image clocks (A)

storage clocks (B)

register clocks (C) 2

summing gate (SG)

reset gate (RG)

1 Tp = 1 clock period

2 Duty cycle = 50% and phase shift of the C clocks is 120 degrees.

MIN.

0

0

2

10

10

3

3

3

TYPICAL

18

450

5

20

20

5

5

5

MAX.

40

1000

1/6 Tp

1/6 Tp

1/6 Tp

UNIT

MHz

kHz

µs

ns

ns

ns

ns

ns

Line Timing

H

SSC

L

H

B1

L

H

B2

L

H

B3

L

H

B4

L

H

CR

L

H

AHigh*

L

H

VD

L

H

BLC

L

19Tp

25Tp

105Tp

14Tp

15Tp

24Tp 15Tp

2 Tp

34Tp

15Tp

101Tp

105Tp

30Tp

141Tp

Pixel Timing

H

SSC

L

H

C1

L

H

C2

L

H

C3

L

H

SG

L

H

RG

L

1079 pixels

1Tp

Tp / 6

Tp = 1 clock period = 1 / 18MHz = 55.56ns

Pixel output sequence: 7 dummy, 20 black, 4 timing, 1024 active, 4 timing, 20 black

* During AHigh = H the phiA high level is increased from 10V to 14V

Line Time: 1184 x Tp = 65.7µs

VD: Frame pulse

CR: Charge Reset

BLC: Black Level Clamp

B1 to B4: Vertical storage clocks

C1 to C3: Horizontal register clocks

SSC: Start-Stop C-clocks

SG: Summing gate

RG: Reset gate

Figure 3 - Line and pixel timing diagrams

1999 September

6