HD74LV166ATELL データシートの表示(PDF) - Renesas Electronics

部品番号

コンポーネント説明

メーカー

HD74LV166ATELL Datasheet PDF : 10 Pages

| |||

Preliminary Datasheet

HD74LV166A

Parallel-Load 8-bit Shift Register

R04DS0002EJ0400

(Previous: REJ03D0321-0300)

Rev.4.00

Aug 16, 2010

Description

The HD74LV166A is 8-bit shift register with an output from the last stage. Data may be loaded into the register either

in parallel or in serial form. When the Shift/Load input is low, the data is loaded asynchronously in parallel. When the

Shift/Load input is high, the data is loaded serially on the rising edge of either clock inhibit or Clock. Clear is

asynchronous and active-low.

The 2-input NOR clock may be used either by combining two independent clock sources or by designating one of the

clock inputs to act as a clock inhibit.

Low-voltage and high-speed operation is suitable for the battery-powered products (e.g., notebook computers), and the

low-power consumption extends the battery life.

Features

VCC = 2.0 V to 5.5 V operation

All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V)

All outputs VO (Max.) = 5.5 V (@VCC = 0 V)

Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

Typical VOH undershoot > 2.3 V (@VCC = 3.3 V, Ta = 25°C)

Output current ±6 mA (@VCC = 3.0 V to 3.6 V), ±12 mA (@VCC = 4.5 V to 5.5 V)

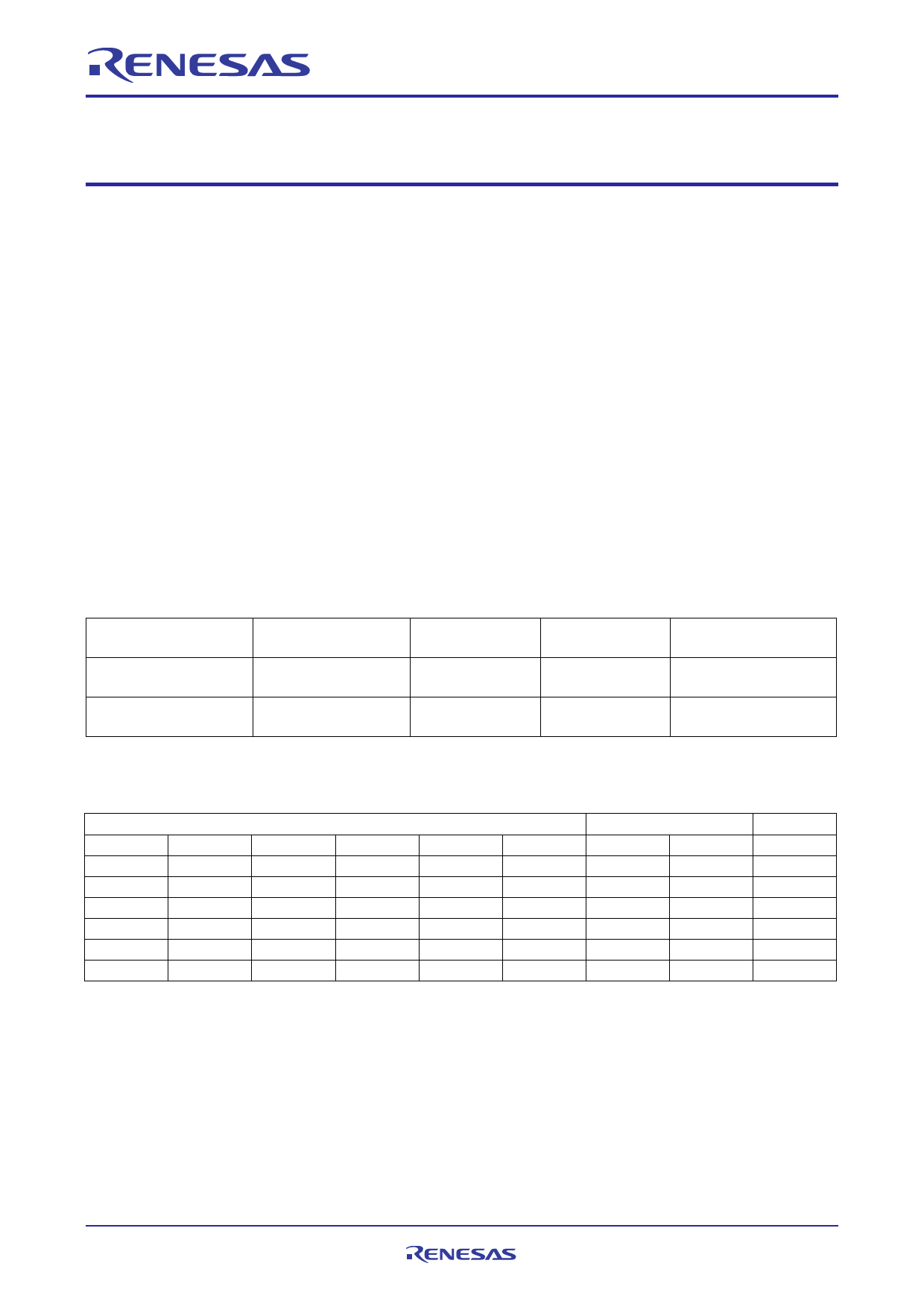

Ordering Information

Part Name

Package Type

Package Code

(Previous Code)

Package

Abbreviation

HD74LV166AFPEL

SOP–16 pin(JEITA)

PRSP0016DH-B FP

(FP–16DAV)

HD74LV166ATELL

TSSOP–16 pin

PTSP0016JB-A T

(TTP–16DAV)

Note: Please consult the sales office for the above package availability.

Taping Abbreviation

(Quantity)

EL (2,000 pcs/reel)

ELL (2,000 pcs/reel)

Function Table

CLR

SH/LD

Inputs

CLK INH

CLK

SER

A ... H

Internal outputs

QA

QB

L

X

X

X

X

X

L

L

H

X

L

L

X

X

QA0

QB0

H

L

L

X

a ... h

a

b

H

H

L

H

X

H

QAn

H

H

L

L

X

L

QAn

H

X

H

X

X

QA0

QB0

Note: H: High level

L: Low level

: Low to high transition

X: Immaterial

a ... h: Parallel data

QA0 ... QH0: Outputs remain unchanged.

QAn ... QGn: Data shifted from the previous stage on a positive edge at the clock input.

Output

QH

L

QH0

h

QGn

QGn

QH0

R04DS0002EJ0400 Rev.4.00

Aug 16, 2010

Page 1 of 9