HN58V256A гғҮгғјгӮҝгӮ·гғјгғҲгҒ®иЎЁзӨәпјҲPDFпјү - Renesas Electronics

йғЁе“Ғз•ӘеҸ·

гӮігғігғқгғјгғҚгғігғҲиӘ¬жҳҺ

гғЎгғјгӮ«гғј

HN58V256A Datasheet PDF : 25 Pages

| |||

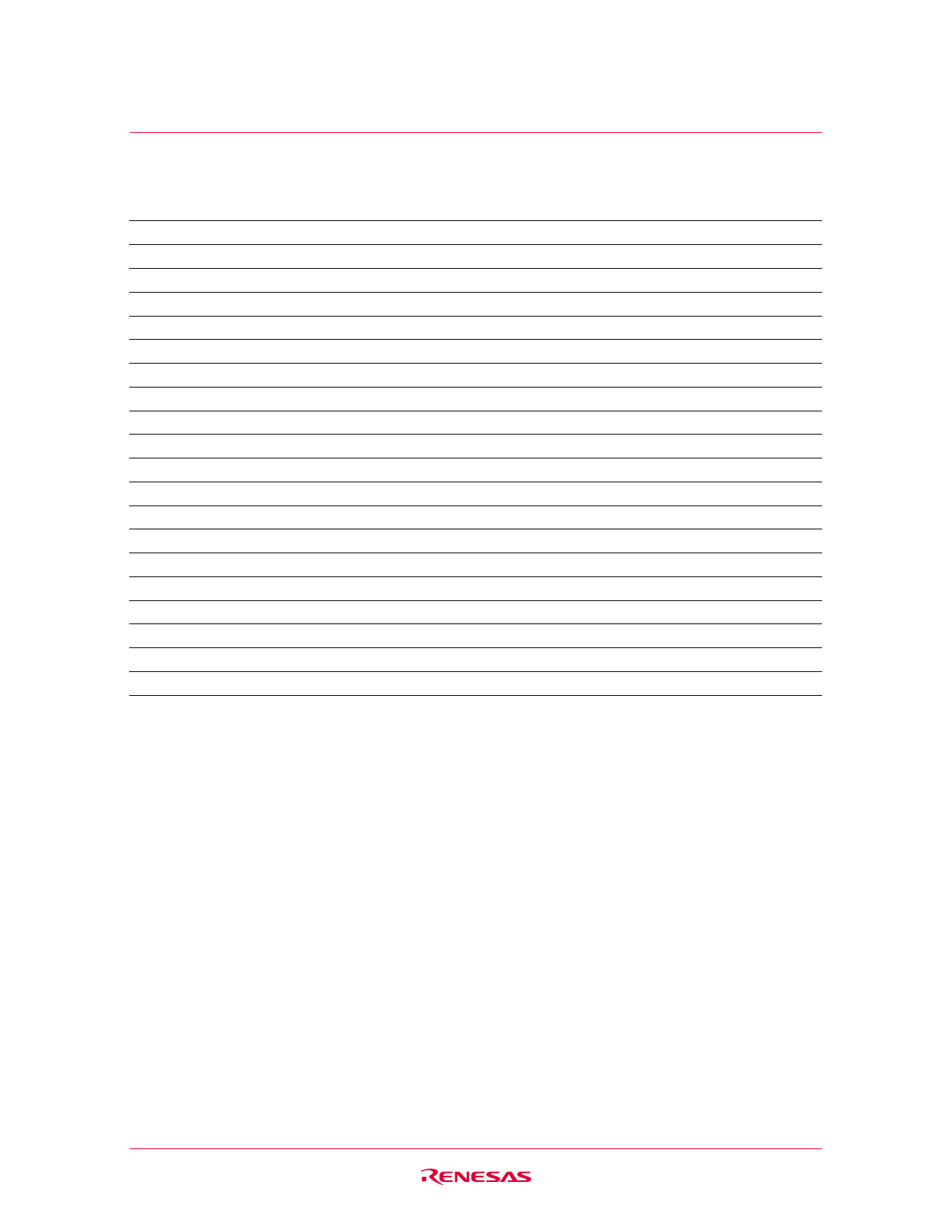

HN58V256A Series, HN58V257A Series

Write Cycle

Parameter

Symbol Min*3 Typ Max Unit Test conditions

Address setup time

tAS

0

пЈ§

пЈ§

ns

Address hold time

tAH

50

пЈ§

пЈ§

ns

CE to write setup time (WE controlled)

tCS

0

пЈ§

пЈ§

ns

CE hold time (WE controlled)

tCH

0

пЈ§

пЈ§

ns

WE to write setup time (CE controlled)

tWS

0

пЈ§

пЈ§

ns

WE hold time (CE controlled)

tWH

0

пЈ§

пЈ§

ns

OE to write setup time

tOES

0

пЈ§

пЈ§

ns

OE hold time

tOEH

0

пЈ§

пЈ§

ns

Data setup time

tDS

70

пЈ§

пЈ§

ns

Data hold time

tDH

0

пЈ§

вҖ”

ns

WE pulse width (WE controlled)

tWP

200 пЈ§

пЈ§

ns

CE pulse width (CE controlled)

tCW

200 пЈ§

пЈ§

ns

Data latch time

tDL

100 пЈ§

пЈ§

ns

Byte load cycle

tBLC

0.3 пЈ§

30

Вөs

Byte load window

Write cycle time

tBL

100 пЈ§

пЈ§

Вөs

tWC

пЈ§

пЈ§

10*4 ms

Time to device busy

Write start time

Reset protect time*2

Reset high time*2, 6

tDB

120 пЈ§

пЈ§

ns

tDW

0*5

пЈ§

пЈ§

ns

tRP

100 пЈ§

пЈ§

Вөs

tRES

1

пЈ§

пЈ§

Вөs

Notes: 1. tDF and tDFR are defined as the time at which the outputs achieve the open circuit conditions and are

no longer driven.

2. This function is supported by only the HN58V257A series.

3. Use this device in longer cycle than this value.

4. tWC must be longer than this value unless polling techniques or RDY/Busy (only the HN58V257A

series) are used. This device automatically completes the internal write operation within this value.

5. Next read or write operation can be initiated after tDW if polling techniques or RDY/Busy (only the

HN58V257A series) are used.

6. This parameter is sampled and not 100% tested.

7. A6 through A14 are page addresses and these addresses are latched at the first falling edge of

WE.

8. A6 through A14 are page addresses and these addresses are latched at the first falling edge of

CE.

9. See AC read characteristics.

Rev.5.00, Nov. 17.2003, page 7 of 22