HY27UF081G2M-T データシートの表示(PDF) - Hynix Semiconductor

部品番号

コンポーネント説明

メーカー

HY27UF081G2M-T Datasheet PDF : 48 Pages

| |||

Preliminary

HY27UF(08/16)1G2M Series

HY27SF(08/16)1G2M Series

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash

1. SUMMARY DESCRIPTION

The HYNIX HY27(U/S)F(08/16)1G2M series is a 128Mx8bit with spare 4Mx8 bit capacity. The device is offered in 1.8V

Vcc Power Supply and in 3.3V Vcc Power Supply.

Its NAND cell provides the most cost-effective solution for the solid state mass storage market.

The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old

data is erased.

The device contains 1024 blocks, composed by 64 pages consisting in two NAND structures of 32 series connected

Flash cells.

A program operation allows to write the 2112-byte page in typical 300us and an erase operation can be performed in

typical 2ms on a 128K-byte(X8 device) block.

Data in the page mode can be read out at 60ns(1) cycle time per word. The I/O pins serve as the ports for address and

data input/output as well as command input. This interface allows a reduced pin count and easy migration towards dif-

ferent densities, without any rearrangement of footprint.

Commands, Data and Addresses are synchronously introduced using CE#, WE#, ALE and CLE input pin.

The on-chip Program/Erase Controller automates all program and erase functions including pulse repetition, where

required, and internal verification and margining of data.

The modifying can be locked using the WP# input pin.

The output pin RB# (open drain buffer) signals the status of the device during each operation. In a system with mul-

tiple memories the RB# pins can be connected all together to provide a global status signal.

Even the write-intensive systems can take advantage of the HY27(U/S)F(08/16)1G2M extended reliability of 100K pro-

gram/erase cycles by providing ECC (Error Correcting Code) with real time mapping-out algorithm.

Optionally the chip could be offered with the CE# don’t care function. This option allows the direct download of the

code from the NAND Flash memory device by a microcontroller, since the CE# transitions do not stop the read opera-

tion.

The copy back function allows the optimization of defective blocks management: when a page program operation fails

the data can be directly programmed in another page inside the same array section without the time consuming serial

data insertion phase.

The cache program feature allows the data insertion in the cache register while the data register is copied into the

flash array. This pipelined program operation improves the program throughput when long files are written inside the

memory.

A cache read feature is also implemented. This feature allows to dramatically improve the read throughput when con-

secutive pages have to be streamed out.

This device includes also extra features like OTP/Unique ID area, Automatic Read at Power Up, Read ID2 extension.

The HYNIX HY27(U/S)F(08/16)1G2M series is available in 48 - TSOP1 12 x 20 mm , 48 - WSOP1 12 x 17 mm,

FBGA 9.5 x 12 mm.

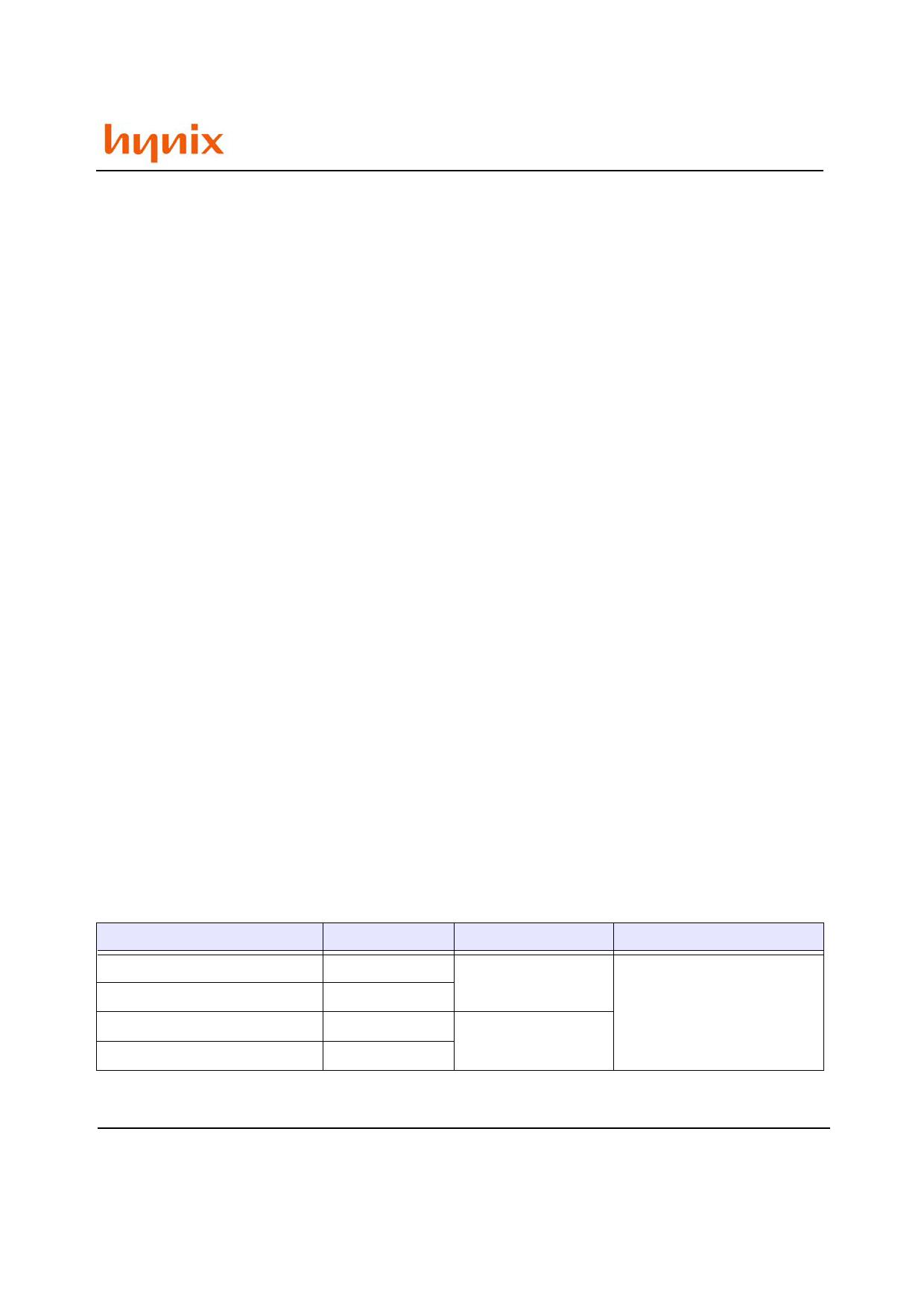

1.1 Product List

PART NUMBER

ORIZATION

HY27SF081G2M

x8

HY27SF161G2M

x16

HY27UF081G2M

x8

HY27UF161G2M

x16

NOTE: 1. This parameters is applied to the errata.

VCC RANGE

1.70 - 1.95 Volt

2.7V - 3.6 Volt

PACKAGE

63FBGA / 48TSOP1 / 48WSOP1

Rev 0.7 / Apr. 2005

4