IDT72200 データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

メーカー

IDT72200

IDT72200 Datasheet PDF : 11 Pages

| |||

IDT72420/72200/72210/72220/72230/72240 CMOS SYNCFIFO™

64 x 8, 256 x 8, 512 x 8, 1,024 x 8, 2,048 x 8, 4,096 x 8

COMMERCIAL TEMPERATURE RANGE

SIGNAL DESCRIPTIONS

INPUTS:

Data In (D0–D7) — Data inputs for 8-bit wide data.

When all the data has been read from the FIFO, the Empty Flag (EF) will

go LOW, inhibiting further read operations. Once a valid write operation has

been accomplished, the Empty Flag (EF) will go HIGH after tREF and a valid

read can begin. Read Enable (REN) is ignored when the FIFO is empty.

CONTROLS:

RESET (RS) — Reset is accomplished whenever the Reset (RS) input is

taken to a LOW state. During reset, both internal read and write pointers are

set to the first location. A reset is required after power up before a write

operation can take place. The Full Flag (FF) and Almost-Full Flag (AF) will

be reset to HIGH after tRSF. The Empty Flag (EF) and Almost-Empty Flag

(AE) will be reset to LOW after tRSF. During reset, the output register is

initialized to all zeros.

WRITE CLOCK (WCLK) — A write cycle is initiated on the LOW-to-HIGH

transition of the Write Clock (WCLK). Data setup and hold times must be met

in respect to the LOW-to-HIGH transition of the Write Clock. The Full Flag

(FF) and Almost-Full Flag (AF) are synchronized with respect to the LOW-

to-HIGH transition of the Write Clock.

The Write and Read Clocks can be asynchronous or coincident.

WRITE ENABLE (WEN) — When Write Enable (WEN) is LOW, data can

be loaded into the input register and RAM array on the LOW-to-HIGH

transition of every Write Clock (WCLK). Data is stored in the RAM array

sequentially and independently of any on-going read operation.

When Write Enable (WEN) is HIGH, the input register holds the previous

data and no new data is allowed to be loaded into the register.

To prevent data overflow, the Full Flag (FF) will go LOW, inhibiting

further write operations. Upon the completion of a valid read cycle, the Full

Flag (FF) will go HIGH after tWFF, allowing a valid write to begin. Write

Enable (WEN) is ignored when the FIFO is full.

READ CLOCK (RCLK) — Data can be read on the outputs on the LOW-to-

HIGH transition of the Read Clock (RCLK). The Empty Flag (EF) and

Almost-Empty flag (AE) are synchronized with respect to the LOW-to-HIGH

transition of the Read Clock.

The Write and Read Clocks can be asynchronous or coincident.

READ ENABLE (REN) — When Read Enable (REN) is LOW, data is read

from the RAM array to the output register on the LOW-to-HIGH transition of

the Read Clock (RCLK).

When Read Enable (REN) is HIGH, the output register holds the

previous data and no new data is allowed to be loaded into the register.

OUTPUT ENABLE (OE) — When Output Enable (OE) is enabled (LOW),

the parallel output buffers receive data from the output register. When

Output Enable (OE) is disabled (HIGH), the Q output data bus is in a high-

impedance state.

OUTPUTS:

FULL FLAG (FF) — The Full Flag (FF) will go LOW, inhibiting further write

operation, when the device is full. If no reads are performed after Reset

(RS), the Full Flag (FF) will go LOW after 64 writes for the IDT72420, 256

writes for the IDT72200, 512 writes for the IDT72210, 1,024 writes for the

IDT72220, 2,048 writes for the IDT72230, and 4,096 writes for the IDT72240.

The Full Flag (FF) is synchronized with respect to the LOW-to-HIGH

transition of the Write Clock (WCLK).

EMPTY FLAG (EF) — The Empty Flag (EF) will go LOW, inhibiting further

read operations, when the read pointer is equal to the write pointer,

indicating the device is empty.

The Empty Flag (EF) is synchronized with respect to the LOW-to-HIGH

transition of the Read Clock (RCLK).

ALMOST-FULL FLAG (AF) — The Almost-Full Flag (AF) will go LOW when

the FIFO reaches the almost-full condition. If no reads are performed after

Reset (RS), the Almost-Full Flag (AF) will go LOW after 57 writes for the

IDT72420, 249 writes for the IDT72200, 505 writes for the IDT72210, 1,017

writes for the IDT72220, 2,041 writes for the IDT72230 and 4,089 writes for

the IDT72240.

The Almost-Full Flag (AF) is synchronized with respect to the LOW-to-

HIGH transition of the Write Clock (WCLK).

ALMOST-EMPTY FLAG (AE) — The Almost-Empty Flag (AE) will go LOW

when the FIFO reaches the almost-empty condition. If no reads are

performed after Reset (RS), the Almost-Empty Flag (AE) will go HIGH after

8 writes for the IDT72420, IDT72200, IDT72210, IDT72220, IDT72230 and

IDT72240.

The Almost-Empty Flag (AE) is synchronized with respect to the LOW-

to-HIGH transition of the Read Clock (RCLK).

DATA OUTPUTS (Q0–Q7) — Data outputs for 8-bit wide data.

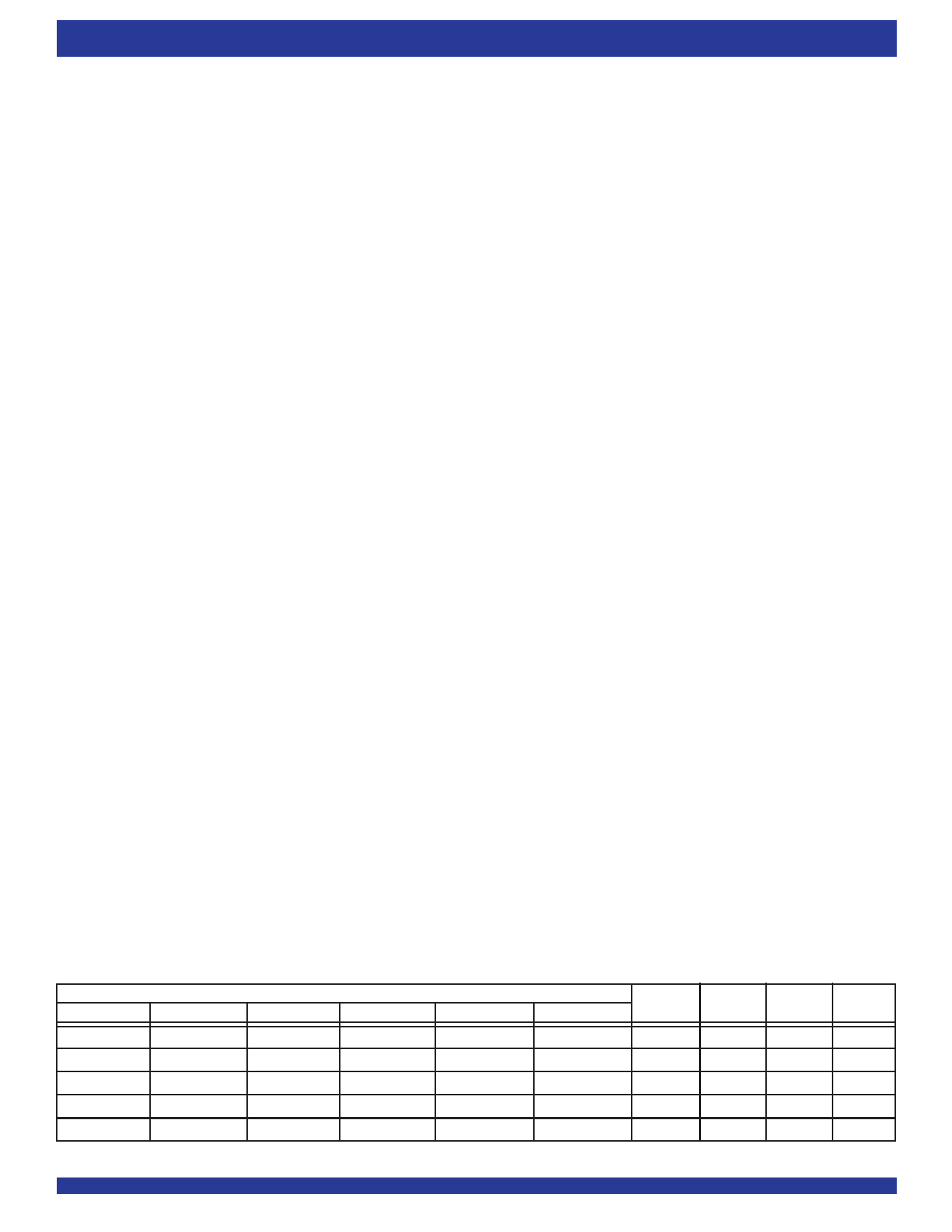

TABLE 1 — STATUS FLAGS

Number of Words in FIFO

IDT72420

IDT72200

IDT72210

IDT72220

IDT72230

IDT72240

FF

AF

AE

EF

0

0

0

0

0

0

H

H

L

L

1 to 7

1 to 7

1 to 7

1 to 7

1 to 7

1 to 7

H

H

L

H

8 to 56

8 to 248

8 to 504

8 to 1,016

8 to 2,040

8 to 4,088

H

H

H

H

57 to 63

249 to 255

505 to 511 1,017 to 1,023 2,041 to 2,047 4,089 to 4,095

H

L

H

H

64

256

512

1,024

2,048

4,096

L

L

H

H

5