LH28F400SUB-Z0 гғҮгғјгӮҝгӮ·гғјгғҲгҒ®иЎЁзӨәпјҲPDFпјү - Sharp Electronics

йғЁе“Ғз•ӘеҸ·

гӮігғігғқгғјгғҚгғігғҲиӘ¬жҳҺ

гғЎгғјгӮ«гғј

LH28F400SUB-Z0 Datasheet PDF : 34 Pages

| |||

LH28F400SUB-Z0

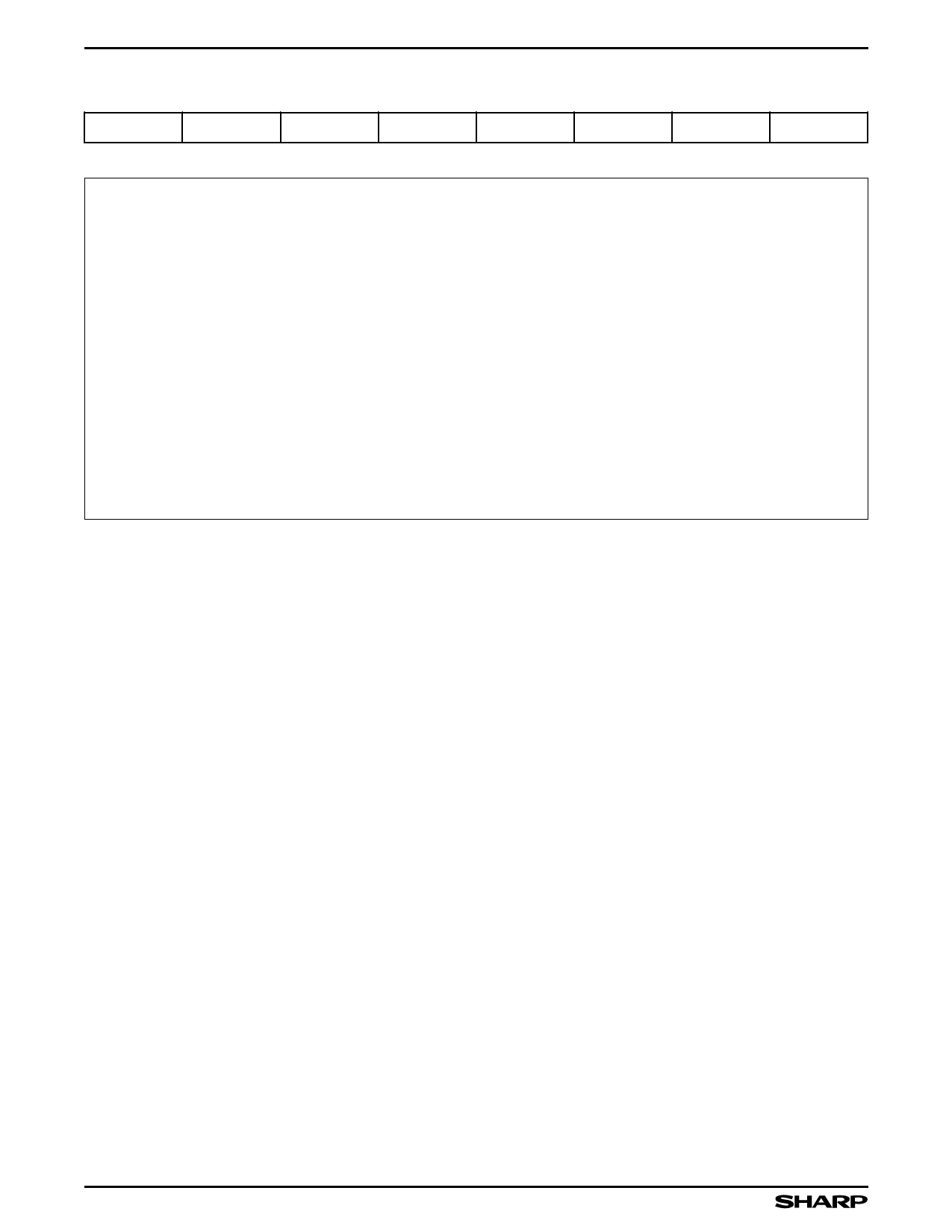

Compatible Status Register

WSMS

ESS

ES

DWS

7

6

5

4

CSR.7 = WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

0 = Busy

CSR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase in Progress/Completed

CSR.5 = ERASE STATUS (ES)

1 = Error in Block Erasure

0 = Successful Block Erase

CSR.4 = DATA-WRITE STATUS (DWS)

1 = Error in Data Write

0 = Data Write Successful

CSR.3 = VPP STATUS (VPPS)

1 = VPP Low Detect, Operation Abort

0 = VPP OK

4M (512K Г— 8, 256K Г— 16) Flash Memory

VPPS

R

R

R

3

2

1

0

NOTES:

1. RY В»/BY В» output or WSMS bit must be checked to determine

completion of an operation (Erase Suspend, Erase or Data

Write) before the appropriate Status bit (ESS, ES or DWS)

is checked for success.

2. If DWS and ES are set to вҖҳ1вҖҷ during an erase attempt, an

improper command sequence was entered. Clear the CSR

and attempt the operation again.

3. The VPPS bit, unlike an A/D converter, does not provide

continuous indication of VPP level. The WSM interrogates

VPPвҖҷs level only after the Data-Write or Erase command

sequences have been entered, and informs the system if

VPP has not been switched on. VPPS is not guaranteed to

report accurate feedback between VPPL and VPPH.

4. CSR.2 - CSR.0 = Reserved for future enhancements.

These bits are reserved for future use and should be

masked out when polling the CSR.

4M FLASH MEMORY

SOFTWARE ALGORITHMS

Overview

With the advanced Command User Interface, its Per-

formance Enhancement commands and Status Regis-

ters, the software code required to perform a given

operation may become more intensive but it will result

in much higher write/erase performance compared with

current flash memory architectures.

The software flowcharts describing how a given

operation proceeds are shown here. Figures 4 through

6 depict flowcharts using the 2nd generation flash de-

vice in the LH28F008SA-compatible mode. Figures 7

through 12 depict flowcharts using the 2nd generation

flash deviceвҖҷs performance enhancement commands

mode.

When the device power-up or the device is reset by

RP В» pin, all blocks come up locked. Therefore, Word/

Byte SerialWrite, Two Byte SerialWrite and Block Erase

can not be performed in each block. However, at that

time, Erase All Unlocked Block is performed normally, if

used, and reflect actual lock status, also the unlocked

block data is erased. When the device power-up or the

device is reset by RP В» pin, Set Write Protect command

must be written to reflect actual block lock status.

Reset Write Protect command must be written be-

fore Write Block Lock command. To reflect actual block

lock status, Set Write Protect command is succeeded.

The Compatible Status Register (CSR) is used to

determine which blocks are locked. In order to see Lock

Status of a certain block, a Word/Byte Write command

(WA = Block Address, WD = FFH) is written to the CUI,

after issuing Set Write Protect command. If CSR.7,

CSR.5 and CSR.4 (WSMS, ES and DWS) are set to

'1's, the block is locked. If CSR.7 is set to '1', the block is

not locked.

Reset Write Protect command enables Write/Erase

operation to each block.

In the case of Block Erase is performed, the block

lock information is also erased. Block Lock command

and Set Write Protect command must be written to pro-

hibit Write/Erase operation to each block.

There are unassigned commands. It is not recom-

mended that the customer use any command other than

the valid commands specified in "Command Bus Defi-

nitionsвҖқ. Sharp reserved the right to redefine these codes

for future functions.

Please do not execute reprogramming 0 for the bit

which has already been programed 0. Overwrite opera-

tion may generate unerasable bit. In case of

reporgramming 0 to the Byte data which has been pro-

gramed 1.

вҖў Program 0 for the bit in which you want to change

data from 1 to 0.

вҖў Program 1 for the bit which has already been pro-

gramed 0.

For example, changing Byte data from 10111101 to

10111100 requires 11111110 programing.

8