IS25LQ032C データシートの表示(PDF) - Integrated Silicon Solution

部品番号

コンポーネント説明

メーカー

IS25LQ032C

IS25LQ032C Datasheet PDF : 54 Pages

| |||

IS25LQ032C

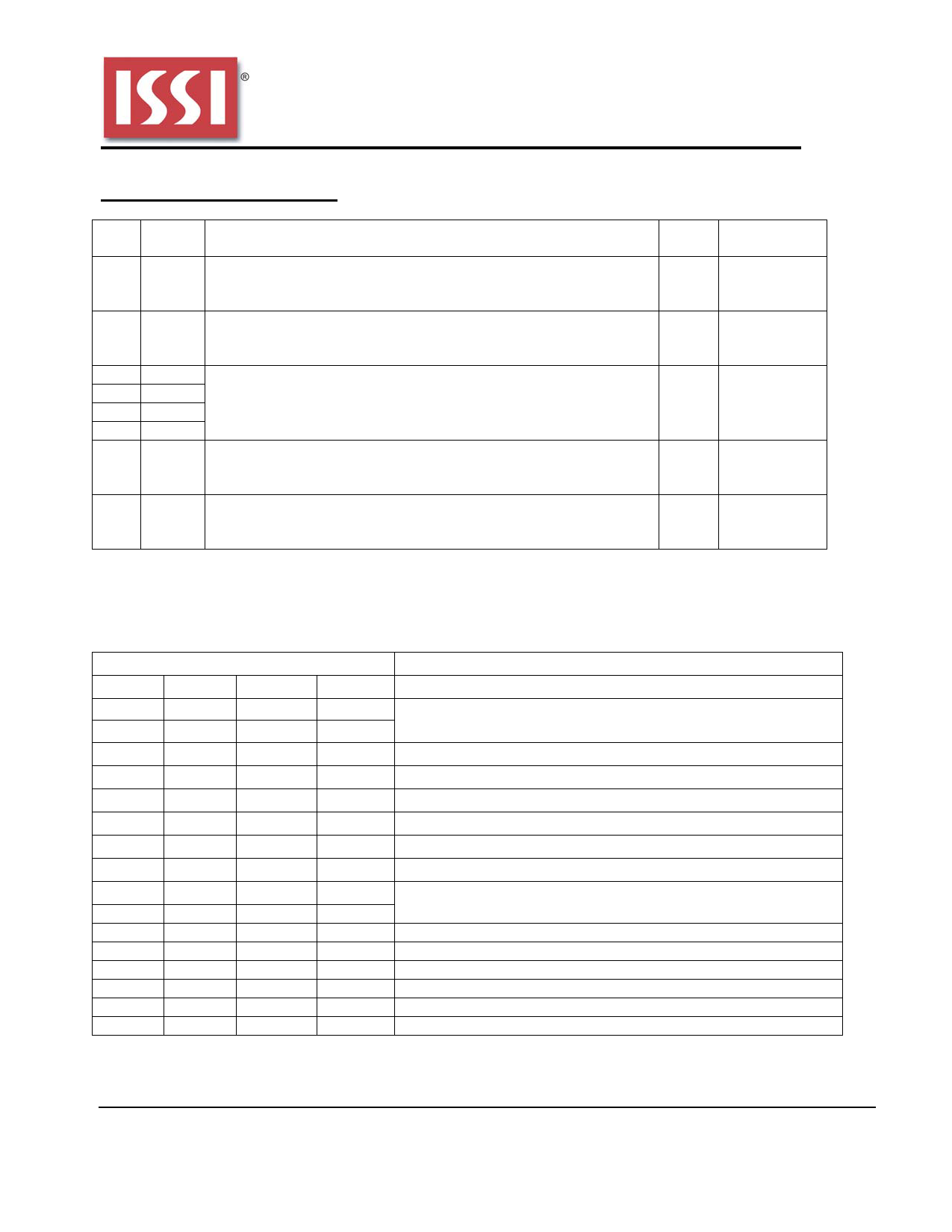

REGISTERS (CONTINUED)

Table 6. Status Register Bit Definition

Bit Name

Definition

Bit 0

Bit 1

Bit 2

Bit 3

Bit 4

Bit 5

Bit 6

Bit 7

WIP

WEL

BP0

BP1

BP2

BP3

QE

SRWD

Write In Progress Bit:

"0" indicates the device is ready

"1" indicates a write cycle is in progress and the device is busy

Write Enable Latch:

"0" indicates the device is not write enabled (default)

"1" indicates the device is write enabled

Block Protection Bit: (See Tables 7, 8 and 9 for details)

"0" indicates the specific blocks are not write-protected (default)

"1" indicates the specific blocks are write-protected

Quad Enable bit:

“0” indicates the Quad output function disable (default)

“1” indicates the Quad output function enable

Status Register Write Disable: (See Table 10 for details)

"0" indicates the Status Register is not write-protected (default)

"1" indicates the Status Register is write-protected

Read-

/Write

R

R/W

R/W

R/W

R/W

Non-Volatile

bit

No

No

Yes

Yes

Yes

Table 7. Block Write Protect Bits for IS25LQ032C

Status Register Bits

BP3

BP2

BP1

BP0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

Protected Memory Area

32 Mbit

None

Upper sixty-forth (1 block : 63th):

Upper thirty-second (2 blocks :62th and 63th):

Upper sixteenth (4 blocks :60th to 63th):

Upper eight (8 blocks :56th to 63th):

Upper quarter (16 blocks :48th to 63th):

Upper half (32 blocks :32th to 63th)

All blocks (64 blocks : 0th to 63th)

(1 blocks :0th):

(2 blocks :0th to 1th):

(4 blocks :0th to 3th):

(8 blocks :0th to 7th):

(16blocks :0th to 15th):

(32 blocks :0th to 31th):

\

Integrated Silicon Solution, Inc.- www.issi.com

Rev. A

9

08/20/2012