KS8001L データシートの表示(PDF) - Micrel

部品番号

コンポーネント説明

メーカー

KS8001L Datasheet PDF : 46 Pages

| |||

Micrel

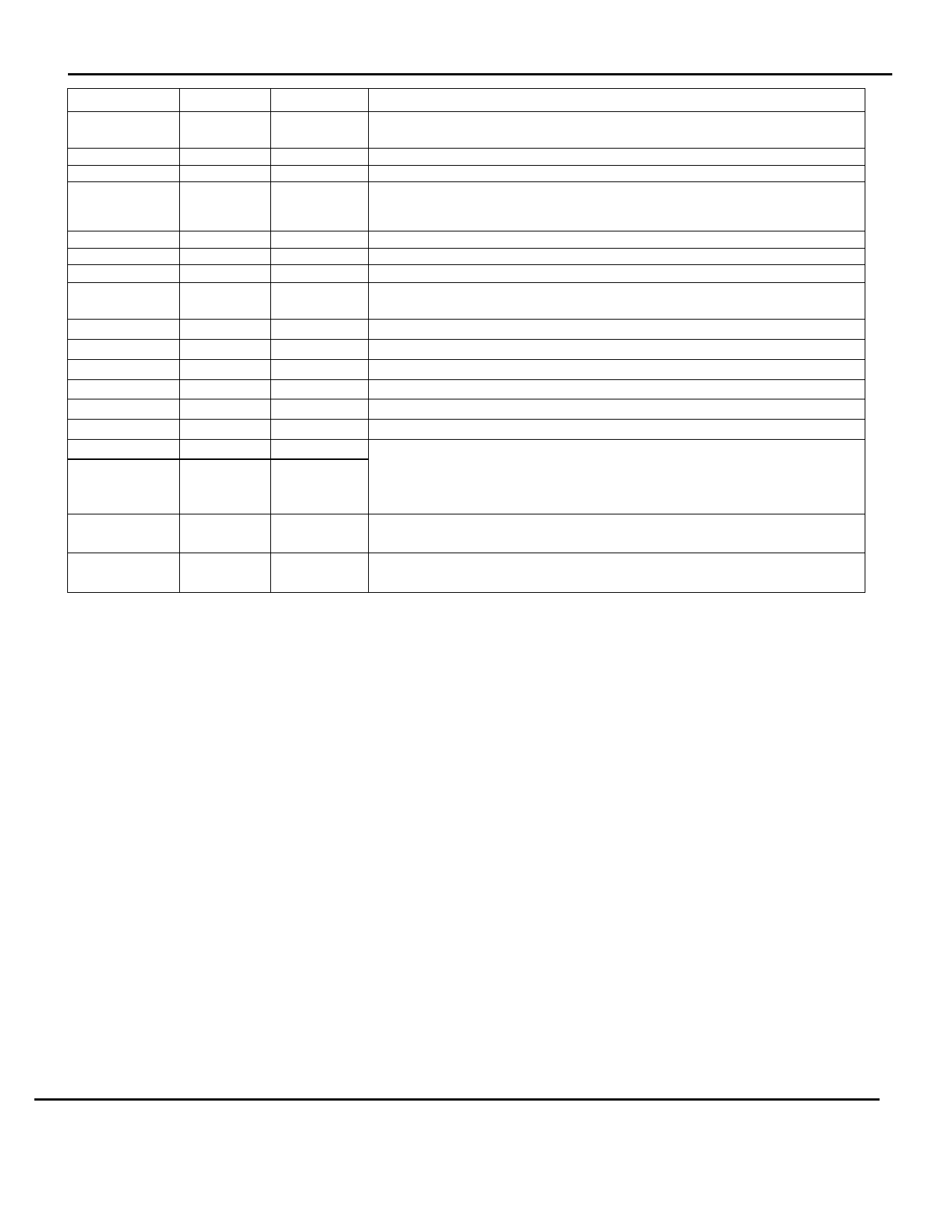

Pin Number

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

Pin Name

VDDRX

RX-

RX+

FXSD/

FXEN

GND

GND

REXT

VDDRCV

GND

TX-

TX+

NC

NC

GND

XO

XI

VDDPLL

RST#

Type (Note 1)

Pwr

I/O

I/O

Ipd/O

Gnd

Gnd

I

Pwr

Gnd

I/O

I/O

Gnd

O

I

Pwr

Ipu

KSZ8001

Pin Function

1.8V analog VDD

(See “Circuit Design Reference for Power Supply” section for details)

Physical receive or transmit ‘-’ differential signal

Physical receive or transmit ‘+’ differential signal

Fiber Mode Enable / Signal Detect in Fiber Mode

If FXEN=0, FX mode is disable. The default is “0”.

(See “100BASE-FX Mode” section for details)

Ground

Ground

Connect a 6.65KΩ external resistor from this pin to ground

3.3V analog VDD

(See “Circuit Design Reference for Power Supply” section for details)

Ground

Physical transmit or receive ‘-’ differential signal

Physical transmit or receive ‘+’ differential signal

No Connect

No Connect

Ground

25MHz crystal/oscillator clock connections

Pins (XI, XO) connect to a crystal. If an oscillator is used, XI connects to a

3.3V tolerant oscillator and XO is a no connect.

Clock is +/- 50ppm for both crystal and oscillator.

1.8V analog PLL VDD

(See “Circuit Design Reference for Power Supply” section for details)

Chip Reset

Active low, minimum of 50 us pulse is required

Note 1:

Pwr = power supply;

Gnd = ground;

I = input;

O = output;

I/O = bi-directional

Ipu = input w/ internal pull up;

Ipd = input w/ internal pull down;

Ipu/O = input w/ internal pull up during

reset, output pin otherwise;

Ipd/O = input w/ internal pull down during

reset, output pin otherwise;

PD = strap pull down;

PU = strap pull up;

Note 2:

MII Rx Mode: The RXD[3..0] bits are synchronous with RXCLK. When RXDV is asserted, RXD [3..0]

presents valid data to MAC through the MII. RXD [3..0] is invalid when RXDV is de-asserted.

Note 3:

RMII Rx Mode: The RXD[1..0] bits are synchronous with REF_CLK. For each clock period in which

CRS_DV is asserted, two bits of recovered data are sent from the PHY.

Note 4:

SMII Rx Mode: Receive data and control information are sent in 10 bit segments. In 100MBit mode, each

segment represents a new byte of data. In 10MBit mode, each segment is repeated ten times; therefore,

every ten segments represents a new byte of data. The MAC can sample any one of every 10 segments in

10MBit mode.

June 2009

Revision 1.04

9