M50LPW012 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M50LPW012 Datasheet PDF : 35 Pages

| |||

M50LPW012

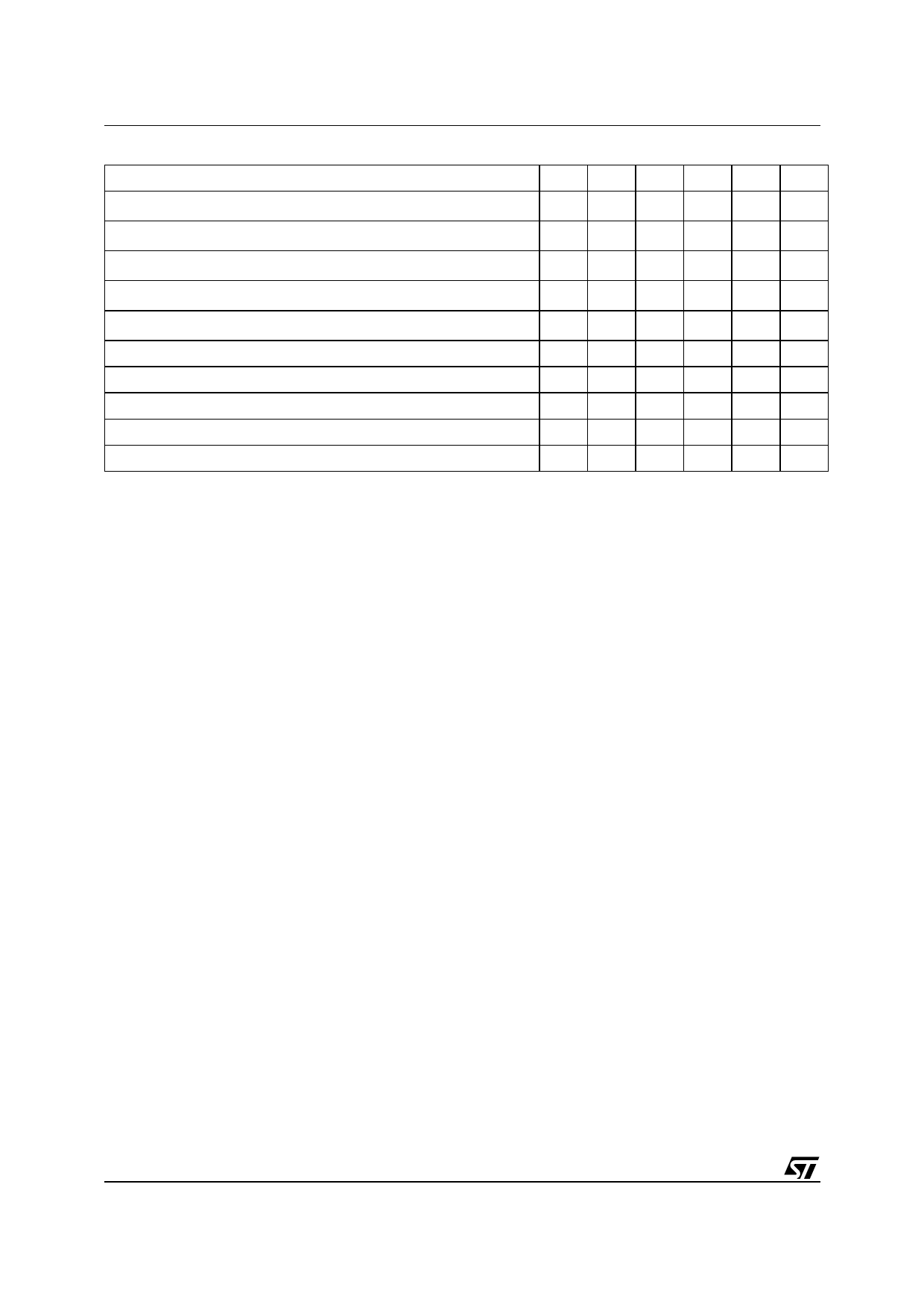

Table 14. Status Register Bits

Operation

Bit 7

Program active

0

Program suspended

1

Program completed successfully

1

Program failure due to Block Protection (LPC Interface only)

1

Program failure due to cell failure

1

Erase active

0

Block Erase suspended

1

Erase completed successfully

1

Block Erase failure due to Block Protection (LPC Interface only)

1

Erase failure due to failed cell(s)

1

Note: 1. For Program operations during Erase Suspend Bit 6 is ‘1’, otherwise Bit 6 is ‘0’.

Bit 6

X(1)

X(1)

X(1)

X(1)

X(1)

0

1

0

0

0

Bit 5

0

0

0

0

0

0

0

0

0

1

Bit 4

0

0

0

0

1

0

0

0

0

0

Bit 2

0

1

0

0

0

0

0

0

0

0

Bit 1

0

0

0

1

0

0

0

0

1

0

After the Program/Erase Controller completes its

operation the Erase Status, Program Status and

Block Protection Status bits should be tested for

errors.

Erase Suspend Status (Bit 6). The Erase Sus-

pend Status bit indicates that a Block Erase oper-

ation has been suspended and is waiting to be

resumed. The Erase Suspend Status should only

be considered valid when the Program/Erase

Controller Status bit is ‘1’ (Program/Erase Control-

ler inactive); after a Program/Erase Suspend com-

mand is issued the memory may still complete the

operation rather than entering the Suspend mode.

When the Erase Suspend Status bit is ‘0’ the Pro-

gram/Erase Controller is active or has completed

its operation; when the bit is ‘1’ a Program/Erase

Suspend command has been issued and the

memory is waiting for a Program/Erase Resume

command.

When a Program/Erase Resume command is is-

sued the Erase Suspend Status bit returns to ‘0’.

Erase Status (Bit 5). The Erase Status bit can be

used to identify if the memory has applied the

maximum number of erase pulses to the block(s)

and still failed to verify that the block(s) has erased

correctly. The Erase Status bit should be read

once the Program/Erase Controller Status bit is ‘1’

(Program/Erase Controller inactive).

When the Erase Status bit is ‘0’ the memory has

successfully verified that the block(s) has erased

correctly; when the Erase Status bit is ‘1’ the Pro-

gram/Erase Controller has applied the maximum

number of pulses to the block(s) and still failed to

verify that the block(s) has erased correctly.

Once the Erase Status bit is set to ‘1’ it can only be

reset to ‘0’ by a Clear Status Register command or

a hardware reset. If it is set to ‘1’ it should be reset

before a new Program or Erase command is is-

sued, otherwise the new command will appear to

fail.

Program Status (Bit 4). The Program Status bit

can be used to identify if the memory has applied

the maximum number of program pulses to the

Byte and still failed to verify that the Byte has pro-

grammed correctly. The Program Status bit should

be read once the Program/Erase Controller Status

bit is ‘1’ (Program/Erase Controller inactive).

When the Program Status bit is ‘0’ the memory has

successfully verified that the Byte has pro-

grammed correctly; when the Program Status bit is

‘1’ the Program/Erase Controller has applied the

maximum number of pulses to the Byte and still

failed to verify that the Byte has programmed cor-

rectly.

Once the Program Status bit is set to ‘1’ it can only

be reset to ‘0’ by a Clear Status Register com-

mand or a hardware reset. If it is set to ‘1’ it should

be reset before a new Program or Erase command

is issued, otherwise the new command will appear

to fail.

Reserved (Bit 3). This status bit is reserved for

future use. Its value should be masked out when-

ever the status register is read.

Program Suspend Status (Bit 2). The Program

Suspend Status bit indicates that a Program oper-

ation has been suspended and is waiting to be re-

sumed. The Program Suspend Status should only

be considered valid when the Program/Erase

Controller Status bit is ‘1’ (Program/Erase Control-

ler inactive); after a Program/Erase Suspend com-

mand is issued the memory may still complete the

operation rather than entering the Suspend mode.

14/35