M50LPW012 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M50LPW012 Datasheet PDF : 35 Pages

| |||

M50LPW012

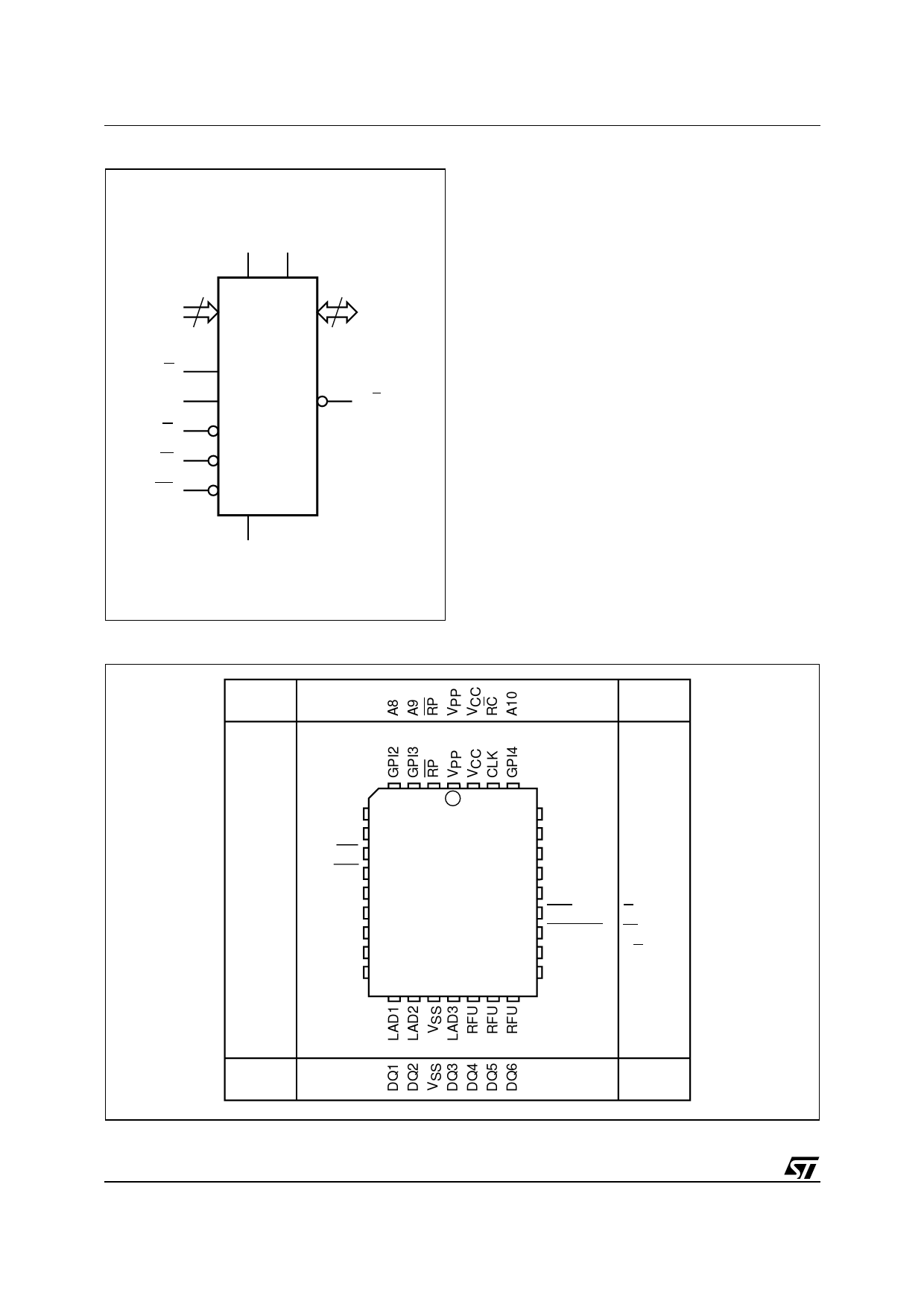

Figure 2. Logic Diagram (A/A Mux Interface)

VCC VPP

11

A0-A10

8

DQ0-DQ7

RC

M50LPW012

IC

RB

G

W

RP

VSS

AI06950

Figure 3. PLCC Connections

A/A Mux

DESCRIPTION

The M50LPW012 is a 2Mbit (256Kb x8) non-

volatile memory that can be read, erased and

reprogrammed. These operations can be

performed using a single low voltage (3.0 to 3.6V)

supply. For fast programming and fast erasing in

production lines an optional 12V power supply can

be used to reduce the programming and the

erasing times.

The memory is divided into blocks that can be

erased independently so it is possible to preserve

valid data while old data is erased. Blocks can be

protected individually to prevent accidental

Program or Erase commands from modifying the

memory. Program and Erase commands are

written to the Command Interface of the memory.

An on-chip Program/Erase Controller simplifies

the process of programming or erasing the

memory by taking care of all of the special

operations that are required to update the memory

contents. The end of a program or erase operation

can be detected and any error conditions

identified. The command set required to control

the memory is consistent with JEDEC standards.

Two different bus interfaces are supported by the

memory. The primary interface is the Low Pin

Count (or LPC) Standard Interface. This has been

designed to remove the need for the ISA bus in

A/A Mux

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

GPI1

GPI0

WP

TBL

ID3 9

ID2

ID1

ID0

LAD0

1 32

M50LPW012

17

IC (VIL)

NC

NC

VSS

25 VCC

INIT

LFRAME

RFU

RFU

IC (VIH)

NC

NC

VSS

VCC

G

W

RB

DQ7

A/A Mux

Note: Pins 27 and 28 are not internally connected.

2/35

A/A Mux

AI06951