M50LPW012 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M50LPW012 Datasheet PDF : 35 Pages

| |||

M50LPW012

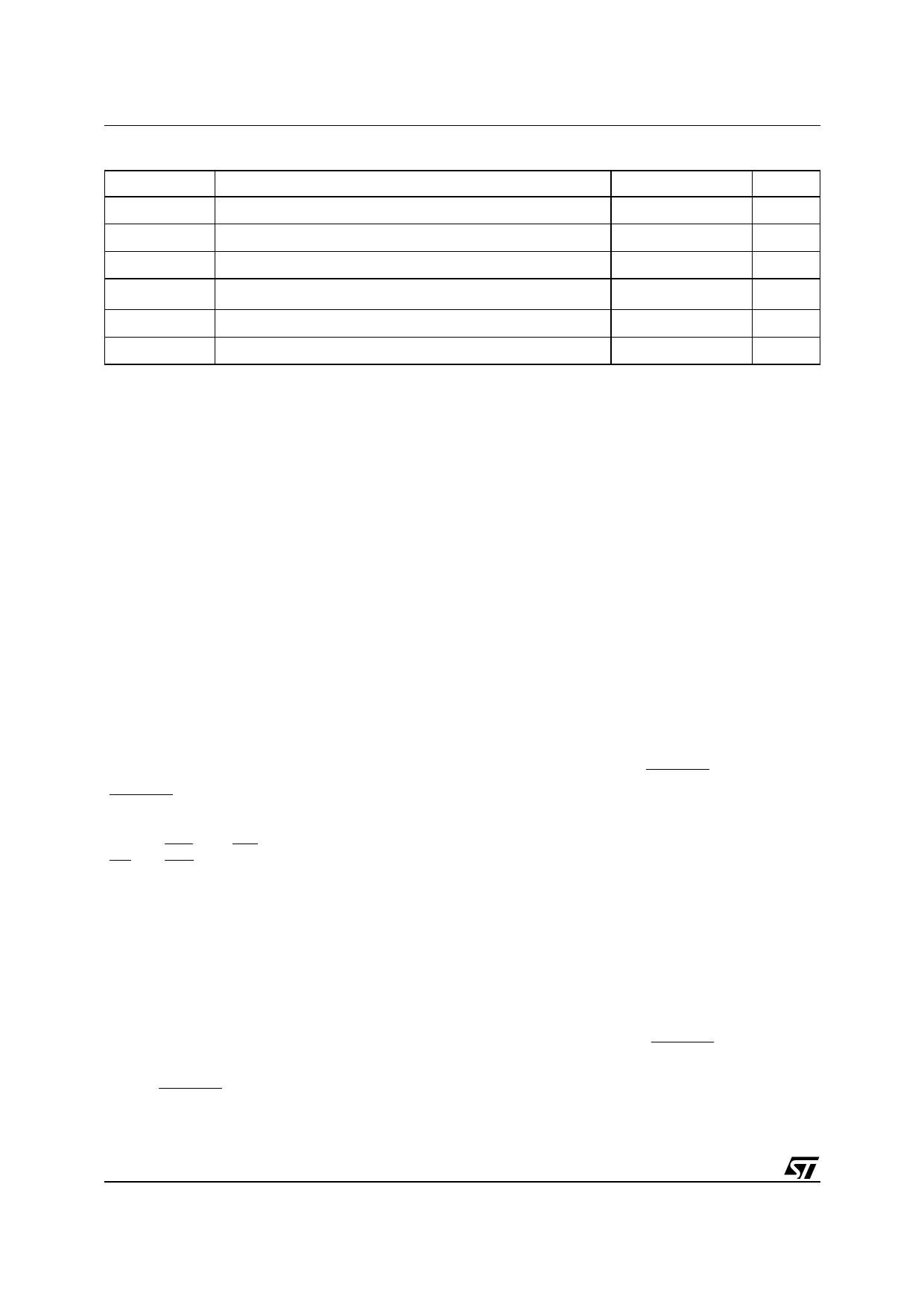

Table 5. Absolute Maximum Ratings (1)

Symbol

Parameter

Value

Unit

TA

Ambient Operating Temperature

0 to 70

°C

TBIAS

Temperature Under Bias

–50 to 125

°C

TSTG

Storage Temperature

–65 to 150

°C

VIO (2)

Input or Output Voltage

–0.6 to VCC + 0.6

V

VCC

Supply Voltage

–0.6 to 4

V

VPP

Program Voltage

–0.6 to 13

V

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may

cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions

above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating condi-

tions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant qual-

ity documents.

2. Minimum Voltage may undershoot to -2V and for less than 20ns during transitions. Maximum Voltage may overshoot to VCC +2V

and for less than 20ns during transitions.

BUS OPERATIONS

The two interfaces have similar bus operations but

the signals and timings are completely different.

The Low Pin Count (LPC) Interface is the usual

interface and all of the functionality of the part is

available through this interface. Only a subset of

functions are available through the Address/

Address Multiplexed (A/A Mux) Interface.

Follow the section Low Pin Count (LPC) Bus

Operations below and the section Address/

Address Multiplexed (A/A Mux) Interface Bus

Operations below for a description of the bus

operations on each interface.

Low Pin Count (LPC) Bus Operations

The Low Pin Count (LPC) Interface consists of

four data signals (LAD0-LAD3), one control line

(LFRAME) and a clock (CLK). In addition

protection against accidental or malicious data

corruption can be achieved using two further

signals (TBL and WP). Finally two reset signals

(RP and INIT) are available to put the memory into

a known state.

The data signals, control signal and clock are

designed to be compatible with PCI electrical

specifications. The interface operates with clock

speeds up to 33MHz.

The following operations can be performed using

the appropriate bus cycles: Bus Read, Bus Write,

Standby, Reset and Block Protection.

Bus Read. Bus Read operations read from the

memory cells, specific registers in the Command

Interface or Low Pin Count Registers. A valid Bus

Read operation starts when Input Communication

Frame, LFRAME, is Low, VIL, as Clock rises and

the correct Start cycle is on LAD0-LAD3. On the

following clock cycles the Host will send the Cycle

Type + Dir, Address and other control bits on

LAD0-LAD3. The memory responds by outputting

Sync data until the wait-states have elapsed

followed by Data0-Data3 and Data4-Data7.

Refer to Table 7, LPC Bus Read Field Definitions,

and Figure 4, LPC Bus Read Waveforms, for a de-

scription of the Field definitions for each clock cy-

cle of the transfer. See Table 23, LPC Interface AC

Signal Timing Characteristics and Figure 9, LPC

Interface AC Signal Timing Waveforms, for details

on the timings of the signals.

Bus Write. Bus Write operations write to the

Command Interface or Low Pin Count Registers. A

valid Bus Write operation starts when Input

Communication Frame, LFRAME, is Low, VIL, as

Clock rises and the correct Start cycle is on LAD0-

LAD3. On the following Clock cycles the Host will

send the Cycle Type + Dir, Address, other control

bits, Data0-Data3 and Data4-Data7 on LAD0-

LAD3. The memory outputs Sync data until the

wait-states have elapsed.

Refer to Table 8, LPC Bus Write Field Definitions,

and Figure 5, LPC Bus Write Waveforms, for a

description of the Field definitions for each clock

cycle of the transfer. See Table 23, LPC Interface

AC Signal Timing Characteristics and Figure 9,

LPC Interface AC Signal Timing Waveforms, for

details on the timings of the signals.

Bus Abort. The Bus Abort operation can be used

to immediately abort the current bus operation. A

Bus Abort occurs when LFRAME is driven Low,

VIL, during the bus operation; the memory will tri-

state the Input/Output Communication pins,

LAD0-LAD3.

6/35