M58MR032-ZCT データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M58MR032-ZCT Datasheet PDF : 52 Pages

| |||

M58MR032C, M58MR032D

DEVICE OPERATIONS

The following operations can be performed using

the appropriate bus cycles: Address Latch, Read

Array (Random, and Page Modes), Write com-

mand, Output Disable, Standby, reset/Power-

down and Block Locking. See Table 4.

Address Latch. In asynchronous operation, the

address is latched on the rising edge of L input. In

burst mode the address is latched either on the ris-

ing edge of L or on the first rising/falling edge of K

(depending on configuration settings) when L is

low.

Read. Read operations are used to output the

contents of the Memory Array, the Electronic Sig-

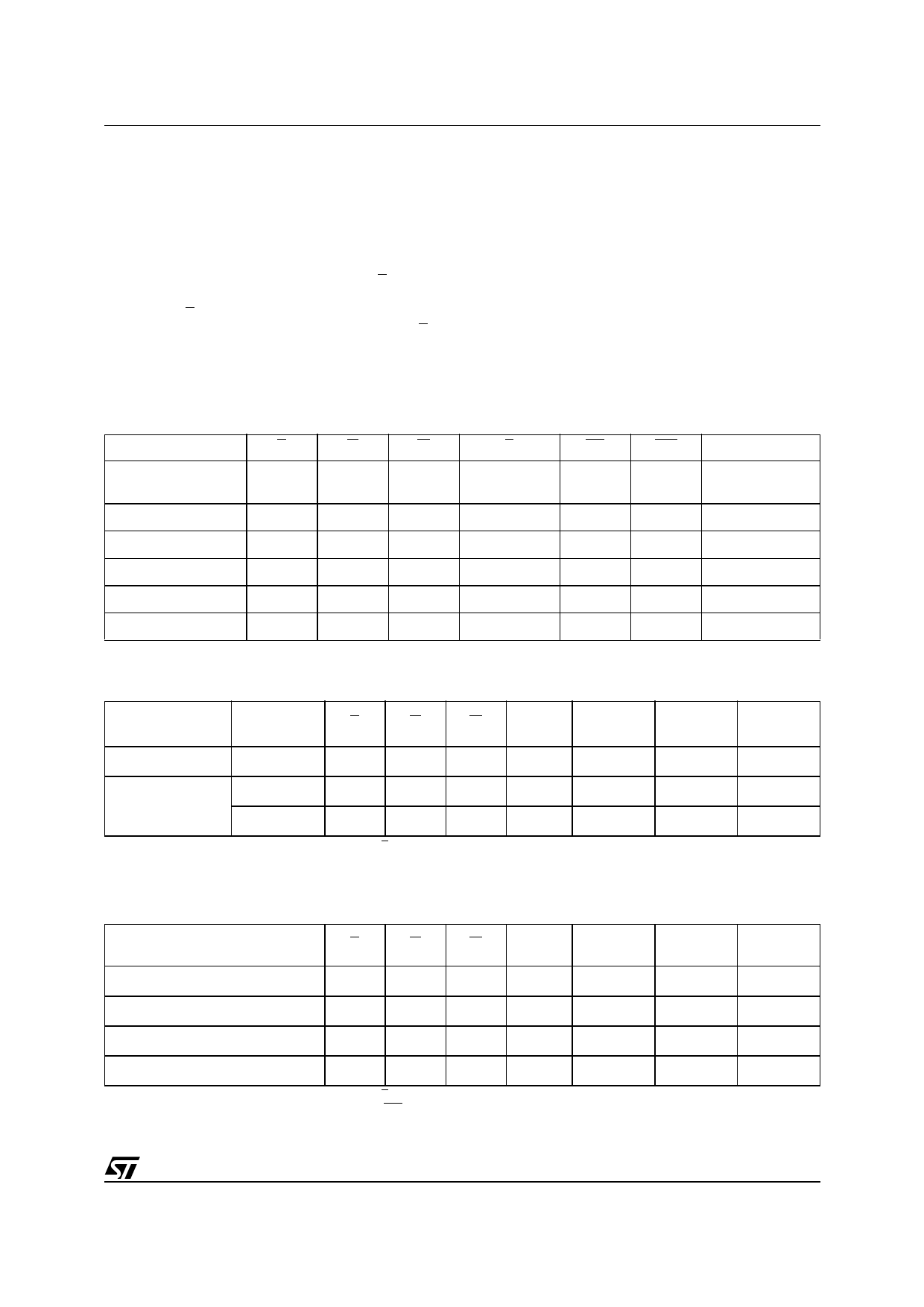

Table 4. User Bus Operations (1)

Operation

E

G

W

Address Latch

VIL

VIH

VIH

Write

VIL

VIH

VIL

Output Disable

VIL

VIH

VIH

Standby

VIH

X

X

Reset / Power-down

X

X

X

Block Locking

VIL

X

X

Note: 1. X = Don’t care.

nature, the Status Register, the CFI, the Block

Protection Status, the Read Configuration Regis-

ter status and the Protection Register.

Read operation of the Memory Array may be per-

formed in asynchronous page mode or synchro-

nous burst mode. In asynchronous page mode

data is internally read and stored in a page buffer.

The page has a size of 4 words and is addressed

by ADQ0 and ADQ1 address inputs.

According to the device configuration the following

Read operations: Electronic Signature - Status

Register - CFI - Block Protection Status - Read

Configuration Register Status - Protection Regis-

ter must be accessed as asynchronous read or as

single synchronous read (see Figure 4).

L

RP

VIL

(rising edge)

VIH

VIH

VIH

VIH

VIH

X

VIH

X

VIL

X

VIH

WP

ADQ15-ADQ0

VIH

Address Input

VIH

Data Input

VIH

Hi-Z

X

Hi-Z

X

Hi-Z

VIL

X

Table 5. Read Electronic Signature (AS and Read CFI instructions) (1)

Code

Device

E

G

W ADQ1 (3) ADQ0 (3)

Manufacturer Code

VIL

VIL

VIH

VIL

VIL

M58MR032C VIL

VIL

VIH

VIL

VIH

Device Code

M58MR032D VIL

VIL

VIH

VIL

VIH

Note: 1. Addresses are latched on the rising edge of L input.

2. EA means Electronic Signature Address (see Read Electronic Signature)

3. Value during address latch.

Other

Address (2)

EA (2)

EA (2)

EA (2)

ADQ15-0

0020h

88DAh

88DBh

Table 6. Read Block Protection (AS and Read CFI instructions) (1)

Block Status

E

G

W

ADQ1 (3) ADQ0 (3)

Other

Address

Protected and unlocked

VIL

VIL

VIH

VIH

VIL

BA (4)

Unprotected and unlocked

VIL

VIL

VIH

VIH

VIL

BA (4)

Protected and locked

VIL

VIL

VIH

VIH

VIL

BA (4)

Unprotected and locked (2)

VIL

VIL

VIH

VIH

VIL

BA (4)

Note: 1. Addresses are latched on the rising edge of L input.

2. A locked block can be unprotected only with WP at VIH.

3. Value during address latch.

4. BA means Block Address. First cycle command address should indicate the bank of the block address.

ADQ15-0

0001

0000

0003

0002

7/52