M5913B1 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M5913B1 Datasheet PDF : 17 Pages

| |||

M5913

FUNCTIONAL DESCRIPTION

The M5913 provides the analog-to-digital and the

digital-to-analog conversion and the transmit and

receive filtering necessary to interface a full du-

plex (4 wires) voice telephone circuit with the

PCM highway of a time division multiplexed

(TDM) system. It is intended to be used at the

analog termination of a PCM line.

The following major functions are provided :

Bandpass filtering of the analog signals prior to

encoding and after decoding

Encoding and decoding of voice and call pro-

gress information

Encoding and decoding of the signaling and

supervision information

GENERAL OPERATION

System Reliability Features

The combo-chip can be powered up by pulsing

FSX and/or FSR while a TTL high voltage is ap-

plied to PDN, provided that all clocks and sup-

plies are connected. The M5913 has internal re-

sets on power up (or when VBB or VCC are

re-applied) in order to ensure validity of the digital

outputs and thereby maintain integrity of the PCM

highway.

On the transmit channel, digital outputs DX and

TS X are held in a high impedance state for ap-

proximately four frames (500µs) after power up or

application of VBB or VCC. After this delay, DX and

TSX will be functional and will occur in the proper

timeslot. The analog circuits on the transmit side

require approximately 40 milliseconds to reach

their equilibrium value due to the autozero circuit

setting time. Thus, valid digital information, such

as for on/off hook detection, is available almost

immediately, while analog information is available

after some delay.

On the receive channel, the digital output SIGR is

also held low for a maximum of four frames after

power up or application of VBB or VCC, SIGR will

remain low thereafter until it is updated by a sig-

naling frame.

To further enhance system reliability, TS X and DX

will be placed in a high impedance state approxi-

mately 20µs after an interruption of CLKX. Simi-

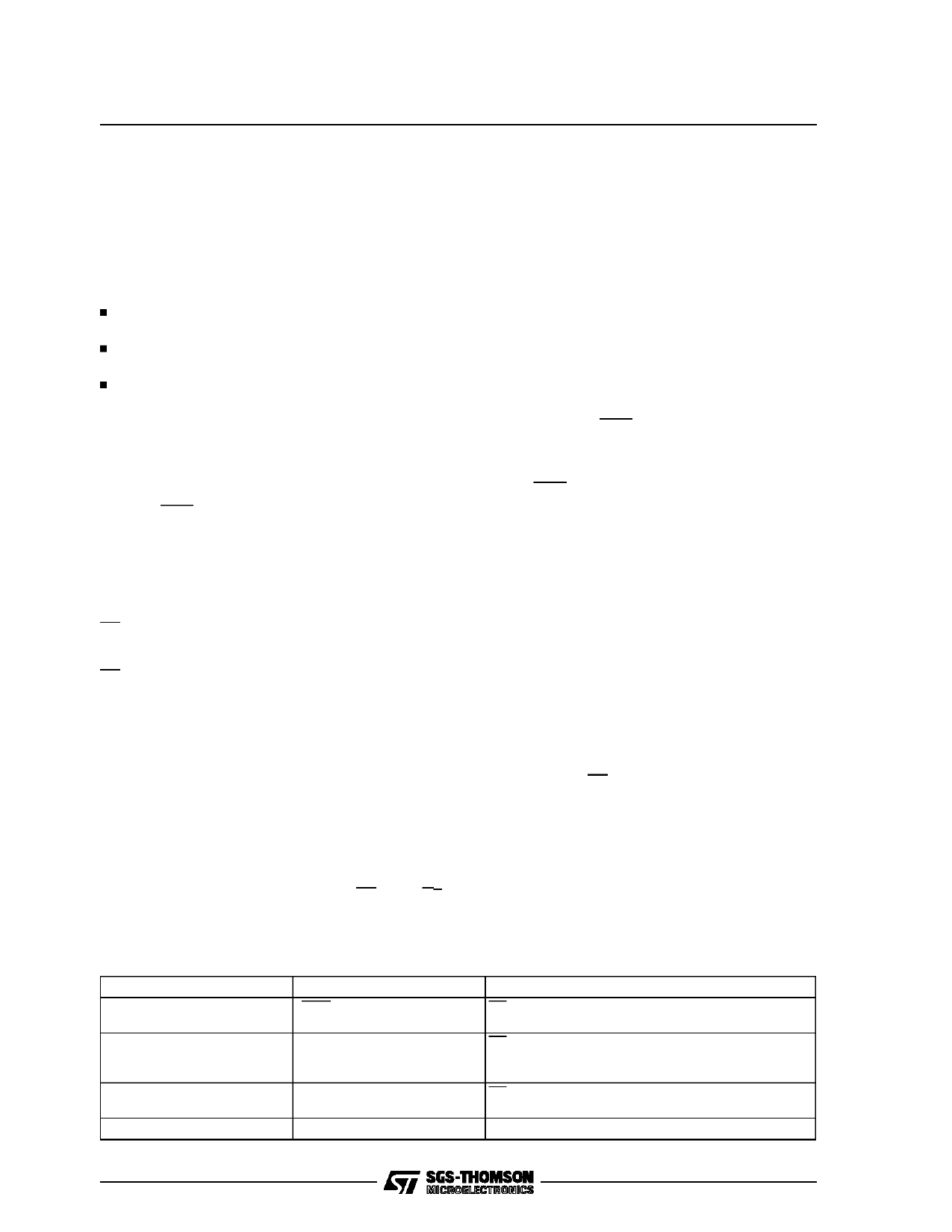

Table 1: Power Down Methods

larly SIGR will be held low approximately 20µs af-

ter an interruption of CLKR. These interruptions

could possibly occur with some kind of fault con-

dition.

Power Down And Standby Modes

To minimize power consumption, two power down

modes are provided in which most M5913 func-

tions are disabled. Only the power down, clock,

and frame sync buffers, which are required to

power up the device, are enabled in these modes.

As shown in table 1, the digital outputs on the ap-

propriate channels are placed in a high imped-

ance state until the device returns to the active

mode.

The Power Down mode utilizes an external con-

trol signal to the PDN pin. In this mode, power

consumption is reduced to an average of 0.5mW.

The device is active when the signal is high and

inactive when it is low. In the absence of any sig-

nal, the PDN pin floats to TTL high allowing the

device to remain active continuously.

The Standby mode leaves the user an option of

powering either channel down separately or pow-

ering the entire down by selectively removing FSX

and/or FSR. With both channels in the standby

state, power consumption is reduced to an aver-

age of 1mW. If transmit only operation is desired,

FSX should be applied to the device while FSR is

held low. Similarly, if receive only operation is de-

sired, FSR should be applied while FSX is held

low.

Fixed Data Rate Mode

Fixed data rate timing, is selected by connecting

DCLKR to VBB. It employs master clock CLKX, and

CLKR, frame synchronization clocks FSX and

FSR, and output TS X.

CLKX, and CLKR, serve both as the master clock

to operate the codec and filter sections and bit

clocks to clock the data in and out from the PCM

highway. FSX and FSR are 8kHz inputs which set

the sampling frequency and distinguish between

signaling and non-signaling frames by thir pulse

width. A frame synchronization pulse which is one

master clock wide designates a non-signaling

frame, while a double wide sync pulse enables

Device Status

Power Down Mode

Stand-by Mode

Power Down Methods

PDN = TTL low

FSX and FSR are TTL low

Only transmit is on stand-by FSX is TTL low

Only receive is on stand-by FSR is TTL low

Digital Outputs Status

TSX and DX are placed in a high impedance state and

SIGR is placed in a TTL low state within 10µs.

TSX and DX are placed in a high impedance state and

SIGR is placed in a TTL low state 30ms after FSX and

FSR are removed.

TSX and DX are placed in a high impedance state

within 30ms.

SIGR is placed in a TTL low state within 30ms.

4/17