M68Z128 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M68Z128 Datasheet PDF : 12 Pages

| |||

M68Z128

5V, 1 Mbit (128Kb x8) Low Power SRAM with Output Enable

s ULTRA LOW DATA RETENTION CURRENT

– 10nA (typical)

– 2.0µA (max)

s OPERATION VOLTAGE: 5V ±10%

s 128Kb x 8 VERY FAST SRAM with OUTPUT

ENABLE

s EQUAL CYCLE and ACCESS TIMES: 55ns

s LOW VCC DATA RETENTION: 2V

s TRI-STATE COMMON I/O

s LOW ACTIVE and STANDBY POWER

s AUTOMATIC POWER-DOWN WHEN

DESELECTED

s INTENDED FOR USE WITH ST

ZEROPOWER® AND TIMEKEEPER®

CONTROLLERS

DESCRIPTION

The M68Z128 is a 1 Mbit (1,048,576 bit) CMOS

SRAM, organized as 131,072 words by 8 bits. The

device features fully static operation requiring no

external clocks or timing strobes, with equal ad-

dress access and cycle times. It requires a single

5V ±10% supply, and all inputs and outputs are

TTL compatible.

Table 1. Signal Names

A0-A16

Address Inputs

DQ0-DQ7

Data Input/Output

E1

Chip Enable 1

E2

Chip Enable 2

G

Output Enable

W

Write Enable

VCC

Supply Voltage

VSS

Ground

NC

Not Connected Internally

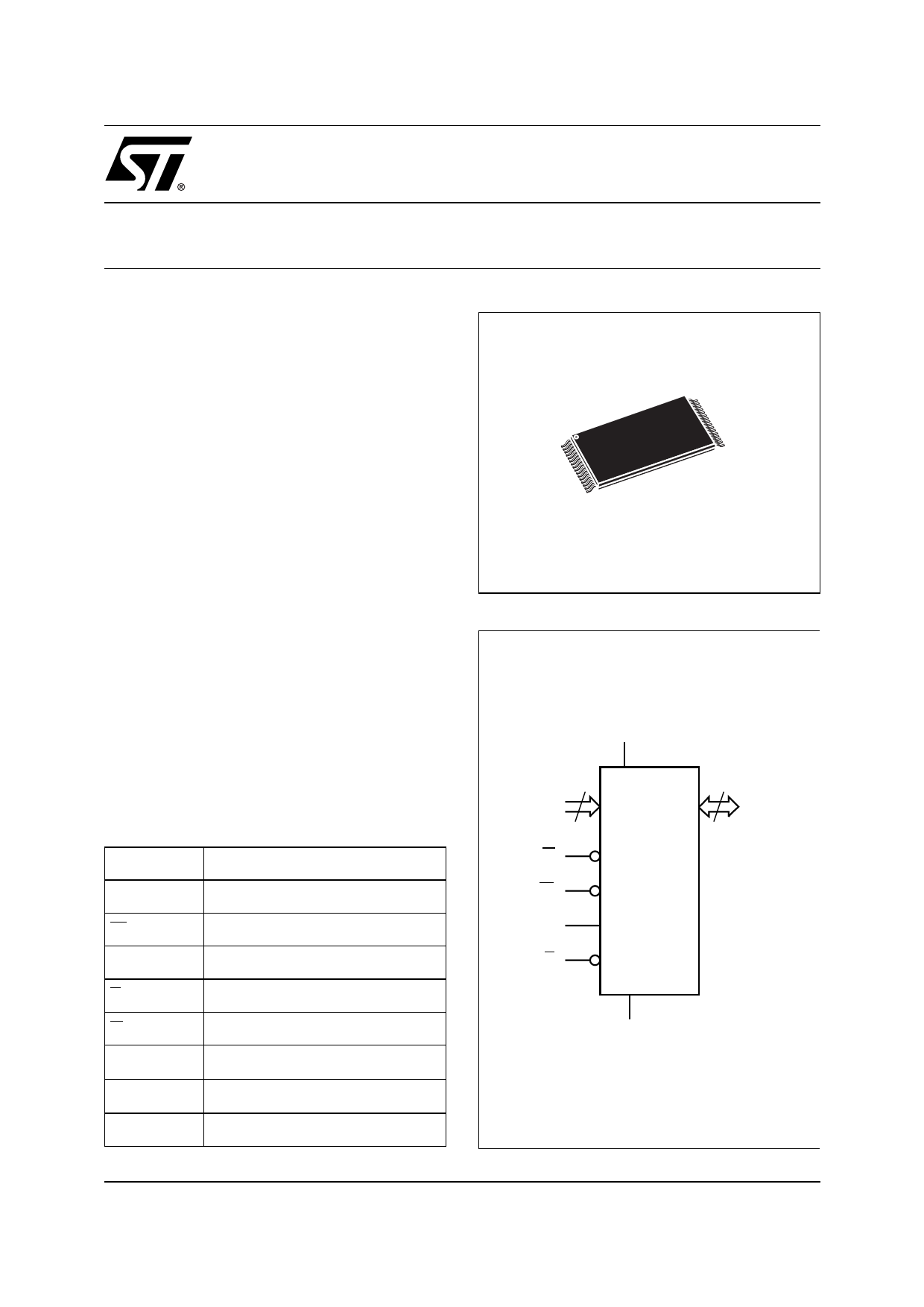

TSOP32 (N)

8 x 20mm

Figure 1. Logic Diagram

VCC

17

A0-A16

8

DQ0-DQ7

W

M68Z128

E1

E2

G

VSS

AI00647

March 2000

1/12