MAX6323(2003) データシートの表示(PDF) - Maxim Integrated

部品番号

コンポーネント説明

メーカー

MAX6323

(Rev.:2003)

(Rev.:2003)

MAX6323 Datasheet PDF : 12 Pages

| |||

µP Supervisory Circuits with Windowed

(Min/Max) Watchdog and Manual Reset

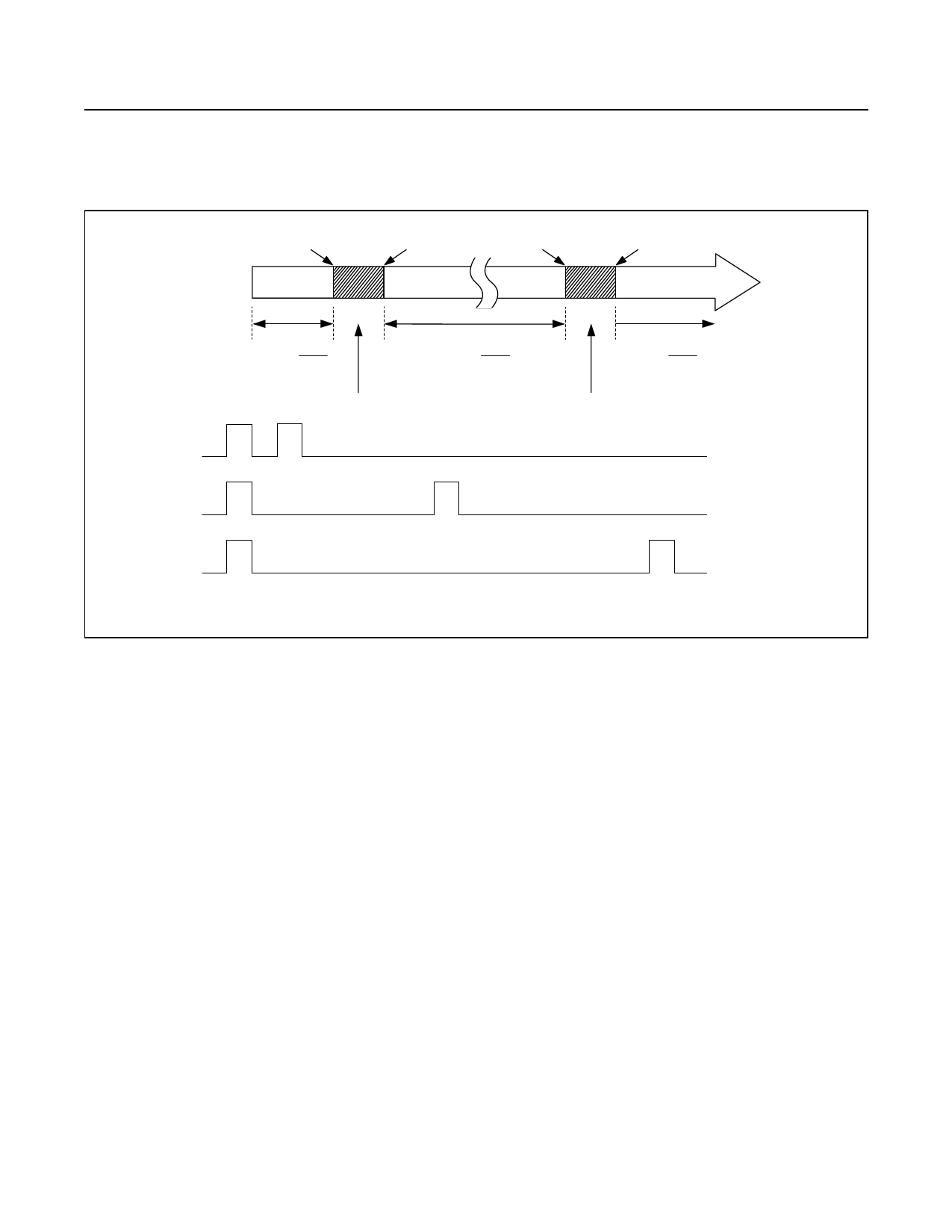

RESET

tWDI < tWD1 (min)

WDI

WDPO

Figure 2. Fast Fault Timing

RESET

FAST FAULT

tWDI < tWD2 (max)

WDI

WDPO

Figure 3. Slow Fault Timing

SLOW FAULT

RESET

tWD1 (max) < tWDI < tWD2 (min)

WDI

H

WDPO L

Figure 4. Normal Operation, WDPO Not Asserted

NORMAL OPERATION (NO PULSING, OUTPUT STAYS HIGH)

_______________________________________________________________________________________ 7