MB91F318A データシートの表示(PDF) - Fujitsu

部品番号

コンポーネント説明

メーカー

MB91F318A Datasheet PDF : 66 Pages

| |||

MB91319 Series

• Built-in multiplier with instruction-level support

32-bit multiplication with sign : 5 cycles

16-bit multiplication with sign : 3 cycles

• Interrupt (PC, PS save) : 6 cycles, 16 priority levels

• Harvard architecture allowing program access and data access to be executed simultaneously

• Instruction prefetch function implemented by a four-word queue in the CPU

• Instruction compatible with FR family

• Bus interface

This bus interface is used for internal macro IF (USB, OSDC)

• CS1, CS2, and CS3 areas are connected as following :

CS1 area : Reserved, CS2 area : USB function, CS3 area : OSDC

• Internal memory

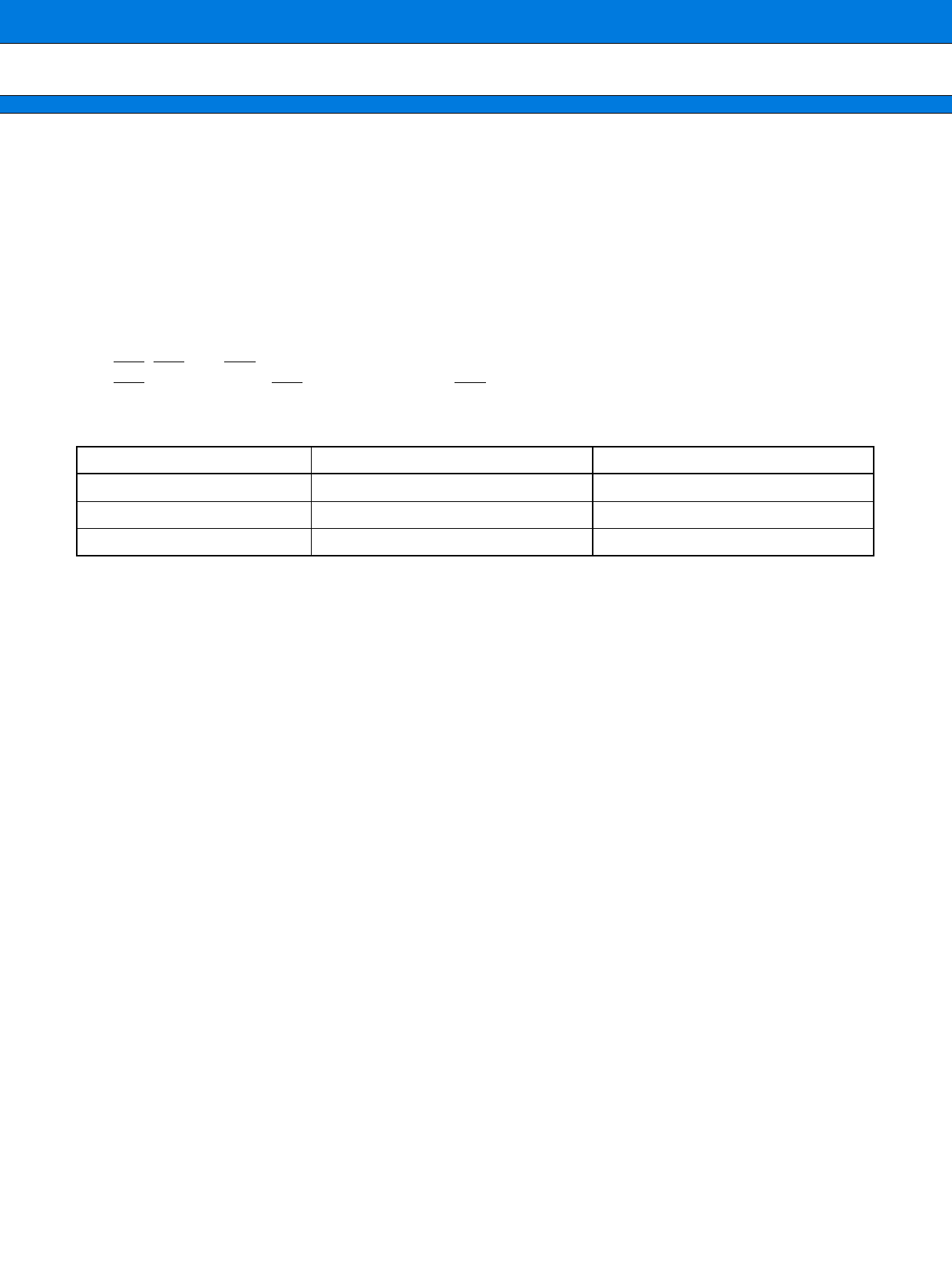

Memory

RAM

FLASH (for program)

Memory for font

MB91FV319A

64 KB

1 MB

512 KB FLASH

MB91F318A

48 KB

1 MB

384 KB MASK ROM

• DMAC (DMA Controller)

• 5 channels (ch0 and ch1 are connected to USB function. )

• Two forwarding factors (internal peripheral/software)

• Specifying of addressing mode 32-bit full address (increased/decreased/fixed)

• Transfer modes (demand transfer, burst transfer, step transfer, block transfer)

• Selectable transfer data size : 8, 16, or 32-bit

• Bit search module (for REALOS)

• Search for the position of the bit “1”/“0”-changed first in one word from the MSB

• Reload timer (including a channel for REALOS)

• 16-bit timer: 3 channels

• The internal clock is selectable from 2/8/32 divisions.

• UART

• Full duplex double buffer

• 5 channels

• Selectable parity ON/OFF

• Asynchronous (start-stop synchronized) or CLK-synchronous communications selectable

• Internal timer for dedicated baud rate

• External clock can be used as transfer clock.

• Assorted error detection functions (for parity, frame, and overrun errors)

(Continued)

2