MF0064M-07AT データシートの表示(PDF) - Mitsumi

部品番号

コンポーネント説明

メーカー

MF0064M-07AT Datasheet PDF : 32 Pages

| |||

MITSUBISHI STORAGE CARD

Preliminary

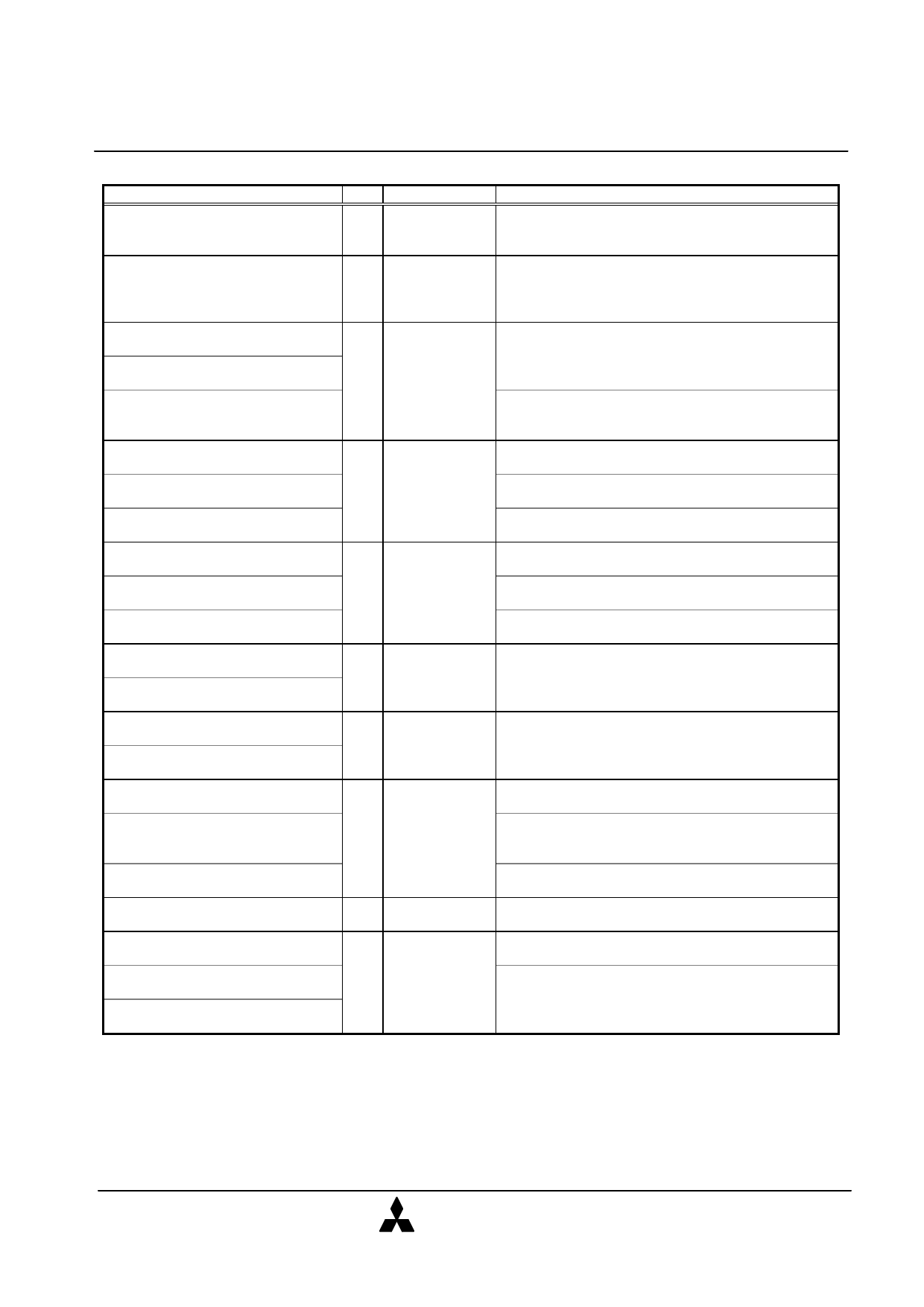

Signal Description

Signal Name

Address bus[A10-A0]

Data bus[D15-D0]

Card Enable[CE1#, CE2#]

(PC Card Memory Mode)

Card Enable[CE1#, CE2#]

(PC Card I/O Mode)

Chip Select[CS0#, CS1#]

(IDE ATA Interface)

Output Enable[OE#]

(PC Card Memory Mode)

Output Enable[OE#]

(PC Card I/O Mode)

ATA SEL#

(IDE ATA Interface)

Write Enable[WE#]

(PC Card Memory Mode)

Write Enable[WE#]

(PC Card I/O Mode)

Write Enable[WE#]

(IDE ATA Interface)

I/O Read[IORD#]

(PC Card I/O Mode)

I/O Read[IORD#]

(IDE ATA Interface)

I/O Write[IOWR#]

(PC Card I/O Mode)

I/O Write[IOWR#]

(IDE ATA Interface)

Ready[READY]

(PC Card Memory Mode)

IREQ#

(PC Card I/O Mode)

INTRQ

(IDE ATA Interface)

Card Detection[CD1#, CD2#]

Write Protect[WP]

(PC Card Memory Mode)

IOIS16#

(PC Card I/O Mode)

IOCS16#

(IDE ATA Interface)

ATA PC CARDS

I/O

Pin No.

I 8, 11, 12, 22,

23, 24, 25, 26,

27, 28, 29

I/O 41, 40, 39, 38,

37, 66, 65, 64,

6, 5, 4, 3,

2 ,32,31, 30

I 7, 42

Description

Signals A10-A0 are address bus. A0 is invalid in

word mode. A10 is the MSB and A0 is the LSB.

Signals D15-D0 are data bus. D0 is the LSB of the

Even Byte of the Word. D8 is the LSB of the Odd Byte

of the Word.

CE1# and CE2# are low active card select signals.

I9

I 15

I 44

I 45

In IDE ATA Interface, CS0# is used to select the

Command Block Registers. CS1# is used to select

the Control Block Registers.

OE# is used to gate Attribute and Common Memory

Read data from the ATA Card.

OE# is used to gate Attribute Memory Read data

from the ATA Card.

To enable IDE ATA Interface, this input should be

grounded by the host.

WE# is used for strobing Attribute and Common

Memory Write data into the ATA Card.

WE# is used for strobing Attribute Memory Write

data into the ATA Card.

This input should be connected Vcc by the host.

IORD# is used to read data from the Card’s I/O

space.

IOWR# is used to write data to the Card’s I/O space.

O 16

O 36, 67

O 33

READY signal is set high when the ATA Card is

ready to accept a new data transfer operation.

This signal of low level is indicates that the card is

requesting software service to host, and high level

indicates that the card is not requesting.

This signal is active high interrupt request to the

host.

CD1# and CD2# provided for proper detection of PC

Card insertion.

This signal is held low because this card does not

have a write protect switch.

This output signal is asserted when the I/O port

address is capable of 16-bit access.

MITSUBISHI

ELECTRIC

3

Oct.1999 Rev. 0.2