ML9261A データシートの表示(PDF) - Oki Electric Industry

部品番号

コンポーネント説明

メーカー

ML9261A Datasheet PDF : 16 Pages

| |||

OKI Semiconductor

FEDL9261A-01

ML9261A

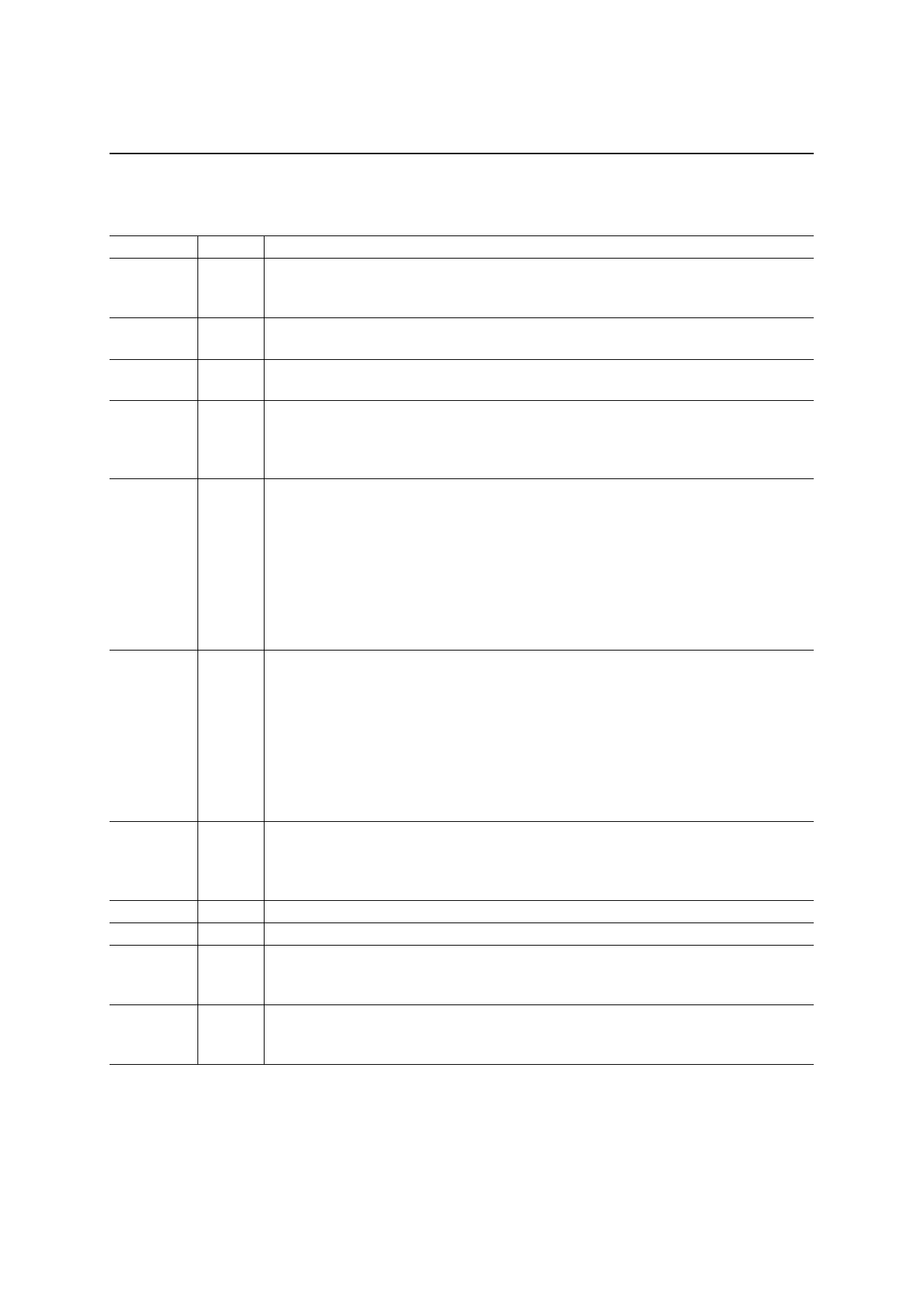

PIN DESCRIPTION

Symbol

CLK

DIN

DOUT

LS

CL

CHG

VHO1-60

VDISP

VDD

D-GND

L-GND

Type

l

I

O

I

I

I

O

Description

Shift register clock input pin.

Shift register reads data from DIN while the CLK pin is low and the data in the shift

register is shifted from one stage to the next stage at the rising edge of the clock.

Serial data input pin of the shift register.

Display data (positive logic) is input in the DIN pin in synchronization with clock.

Serial data output pin of the shift register.

Data is output from the DOUT pin in synchronization with the CLK signal.

Latch strobe input pin.

The contents of the parallel outputs (PO1 to PO60) of the shift register are read at the

rising edge of LS (edge-triggered). When the CLK rises while LS is high, the parallel

outputs (PO1 to PO60) and latch outputs (O1 to O60) go low.

Clear input pin with a built-in pull-down resistor.

The CL pin is normally set high.

If the CL pin is high and the CHG pin is low, the driver outputs (HVO1 to HVO60) are in

phase with the corresponding register outputs (O1 to O60).

If the CL pin is high and the CHG pin is high, the driver outputs (HVO1 to HVO60) are

high irrespective of the states of the register outputs.

If the CL pin is set low, the driver outputs are driven low irrespective of the states of the

CHG pin and register outputs.

This allows display blanking to be set.

Input for testing (with a pull-down resistor).

The CL pin is normally set low.

If the CHG pin is low and the CL pin is high, the driver outputs (HVO1 to HVO60) are in

phase with the corresponding register outputs (O1 to O60).

If the CHG pin is low and the CL pin is low, the driver outputs (HVO1 to HVO60) are low

irrespective of the states of the register outputs.

If the CHG pin is set high, the driver outputs are driven high irrespective of the states of

the register outputs.

This provides the easy testing of all lights after final assembly.

High voltage driver outputs for driving a VFD tube.

If the CL pin is high and the CHG pin is low, the driver outputs are in phase with the

corresponding register outputs (O1 to O60).

The direct connection to the grid or anode of a VFD tube eliminates pull-down resistors.

Power supply pin for VFD tube driver circuits

Power supply pin for logic

GND pin for VFD tube driver circuits.

Since the D-GND pin is not connected internally to the L-GND pin, connect these pins

outside of the IC.

GND pin for the logic circuits.

Since the L-GND pin is not connected internally to the D-GND pin, connect thiese pins

outside of the IC.

4/16