MS81V04160A データシートの表示(PDF) - Oki Electric Industry

部品番号

コンポーネント説明

メーカー

MS81V04160A Datasheet PDF : 24 Pages

| |||

1Semiconductor

FEDS81V04160A-01

MS81V04160A

Read Operation Cycle (MODE2=VSS)

The read operation is controlled by seven control signals, SRCK, RSTR1, RSTR2, RE1, RE2, and OE1, OE2.

Port1 read operation is accomplished by cycling SRCK, and holding RE1 and OE1 high after the read address

pointer reset operation or RSTR1.

Each read operation, which begins after RSTR1, must contain at least 140 active read cycles, i.e. SRCK cycles

while RE1 and OE1 are high.

These operations are the same for Port1 and Port2.

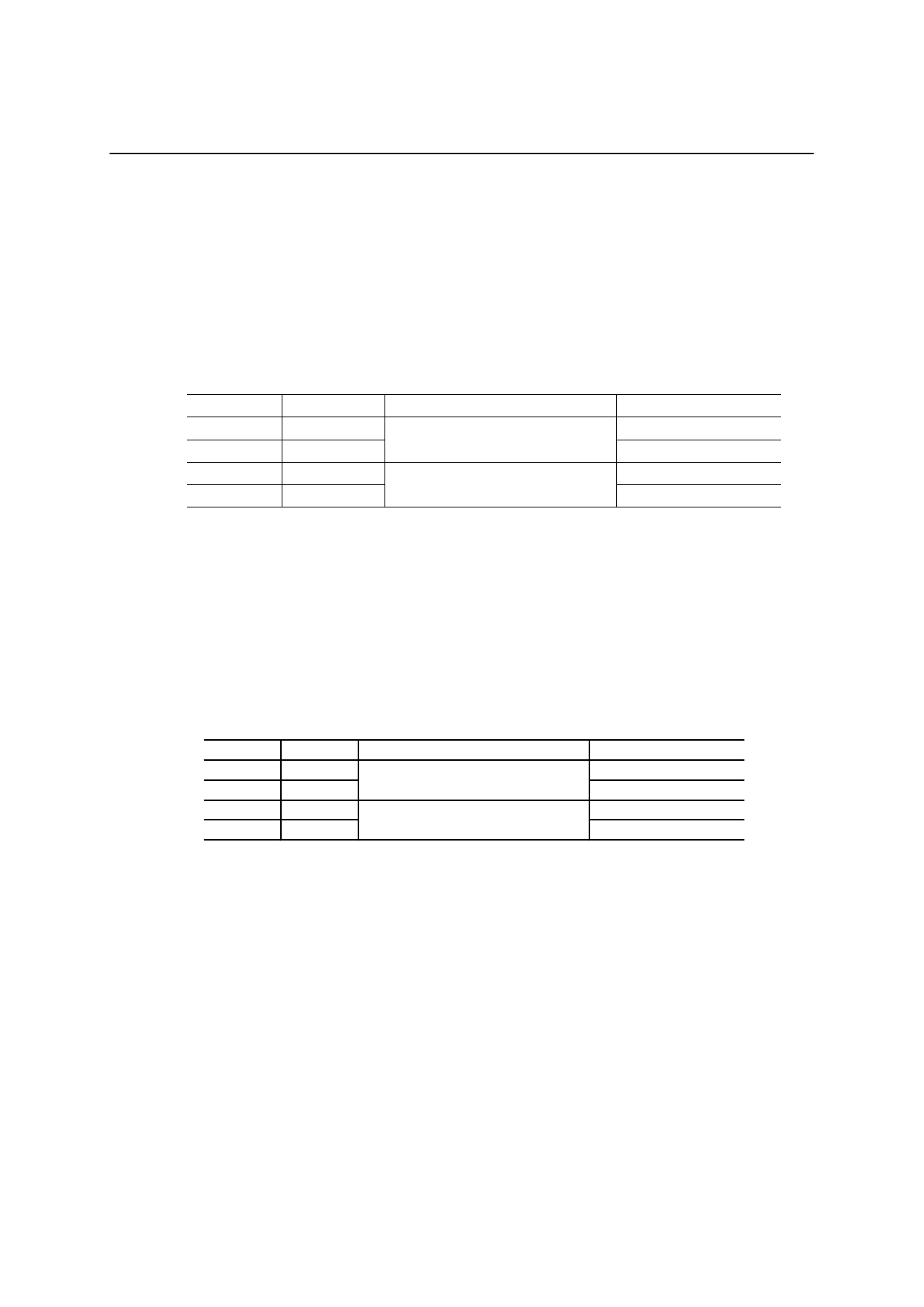

Settings of RE1, 2 and OE1, 2 to the operation mode of read address pointer and Data output.

WE1, 2

H

H

L

L

IE1, 2

H

L

X

L

Internal Write address pointer

Incremented

Halted

Data output

Output

High impedance

Output

High impedance

Read Operation Cycle (MODE2=VCC)

The read operation is controlled by seven control signals, SRCK, RSTR1, RSTR2, RE1, RE2, and OE1, OE2.

Port1 read operation is accomplished by cycling SRCK, and holding RE1 and OE1 low after the read address

pointer reset operation or RSTR1.

Each read operation, which begins after RSTR1, must contain at least 140 active read cycles, i.e. SRCK cycles

while RE1 and OE1 are low.

These operations are the same for Port1 and Port2.

Settings of RE1, 2 and OE1, 2 to the operation mode of read address pointer and Data output.

RE1,2

L

L

H

H

OE1,2

L

H

L

H

Internal Write address pointer

Incremented

Halted

Data output

Output

High impedance

Output

High impedance

11/24