RM5261A データシートの表示(PDF) - PMC-Sierra

部品番号

コンポーネント説明

メーカー

RM5261A Datasheet PDF : 42 Pages

| |||

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

3 Hardware Overview

The RM5261A offers a high-level of integration targeted at high-performance embedded

applications. The key elements of the RM5261A are briefly described below.

3.1 Superscalar Dispatch

The RM5261A has an asymmetric superscalar dispatch unit which allows it to issue an integer

instruction and a floating-point computation instruction simultaneously. Integer instructions

include alu, branch, load/store, and floating-point load/store, while floating-point computation

instructions include floating-point add, subtract, combined multiply-add, and convert. In

combination with its high-throughput fully pipelined floating-point execution unit, the superscalar

capability of the RM5261A provides unparalleled price/performance in computationally intensive

embedded applications.

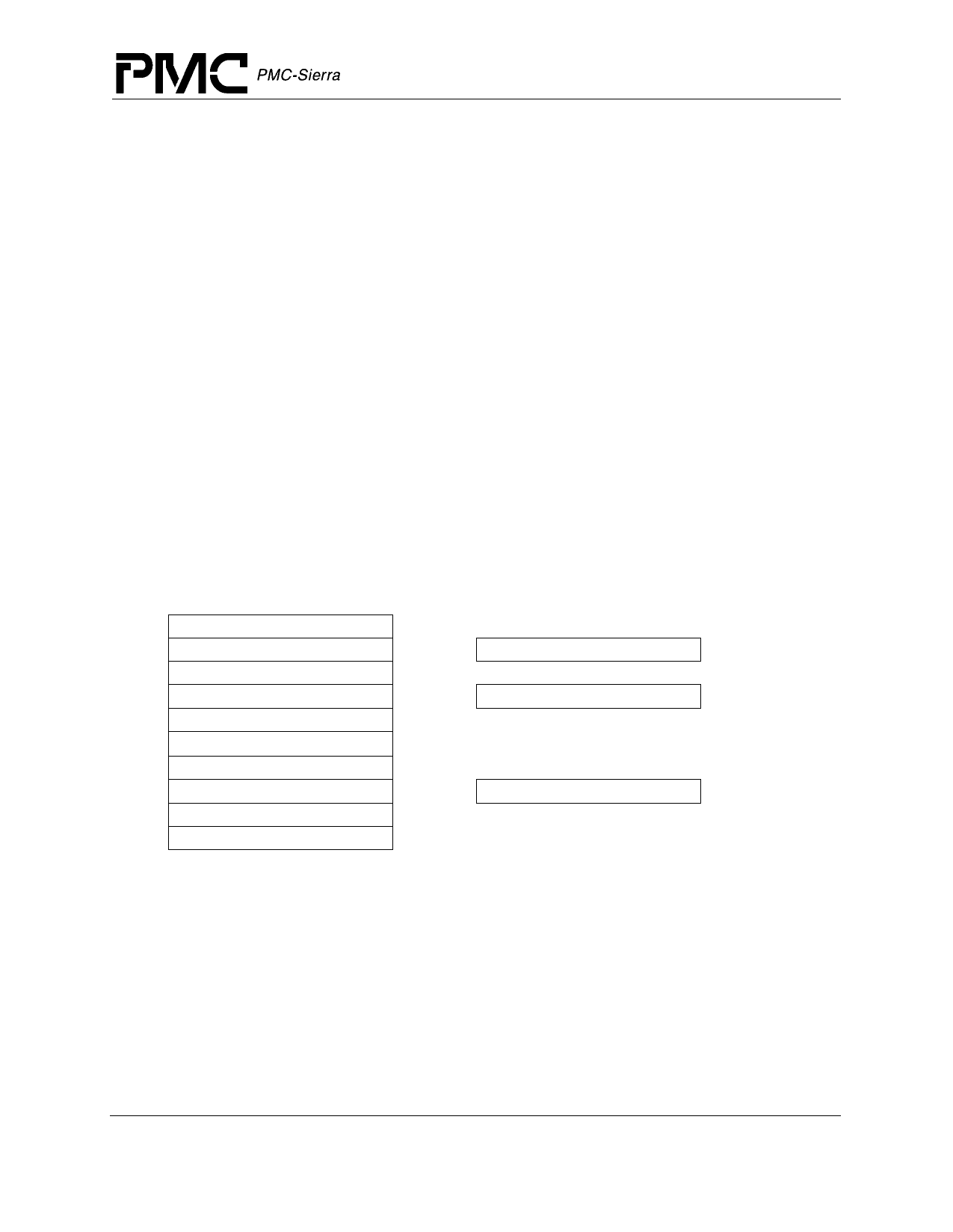

3.2 CPU Registers

The RM5261A CPU contains 32 general purpose registers, two special purpose registers for

integer multiplication and division, a program counter, and no condition code bits. Figure 2 shows

the user visible state.

Figure 2 CPU Registers

General Purpose Registers

63

0

0

r1

r2

•

•

•

•

r29

r30

r31

Multiply/Divide Registers

63

0

HI

63

0

LO

Program Counter

63

0

PC

3.3 Integer Unit

The RM5261A implements the MIPS IV Instruction Set Architecture and is therefore fully upward

compatible with applications that run on processors implementing the earlier generation MIPS I-

III instruction sets. Additionally, the RM5261A includes two implementation specific instructions

not found in the baseline MIPS IV ISA but that are useful in the embedded market place. These

instructions are integer multiply-accumulate (MAD) and 3-operand integer multiply (MUL).

The RM5261A integer unit includes thirty-two general purpose 64-bit registers, a load/store

architecture with single cycle ALU operations (add, sub, logical, shift) and an autonomous

multiply/divide unit. Additional register resources include: the HI/LO result registers for the two-

operand integer multiply/divide operations, and the program counter (PC).

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

11

Document ID: PMC-2002240, Issue 2