MT46V128M8 データシートの表示(PDF) - Micron Technology

部品番号

コンポーネント説明

メーカー

MT46V128M8 Datasheet PDF : 74 Pages

| |||

DOUBLE DATA RATE

(DDR) SDRAM

Features

• VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V

• Bidirectional data strobe (DQS) transmitted/

received with data, i.e., source-synchronous data

capture (x16 has two – one per byte)

• Internal, pipelined double-data-rate (DDR)

architecture; two data accesses per clock cycle

• Differential clock inputs (CK and CK#)

• Commands entered on each positive CK edge

• DQS edge-aligned with data for READs; center-

aligned with data for WRITEs

• DLL to align DQ and DQS transitions with CK

• Four internal banks for concurrent operation

• Data mask (DM) for masking write data (x16 has two

–one per byte)

• Programmable burst lengths: 2, 4, or 8

• Auto Refresh and Self Refresh Modes

• Longer lead TSOP for improved reliability (OCPL)

• 2.5V I/O (SSTL_2 compatible)

• Concurrent auto precharge option is supported

• tRAS lockout supported (tRAP = tRCD)

OPTIONS

MARKING

• Configuration

256 Meg x 4 (64 Meg x 4 x 4 banks)

256M4

128 Meg x 8 (32 Meg x 8 x 4 banks)

128M8

64 Meg x 16 (16 Meg x 16 x 4 banks)

64M16

• Plastic Package – OCPL

66-pin TSOP(400 mil width, 0.65mm TG

pin pitch)

66-pin TSOP Lead-Free (400 mil width,

P

0.65mm pin pitch)

• Timing – Cycle Time

7.5ns @ CL = 2.5 (DDR266B)1, 2

-75

• Temperature Rating

Commercial Temperature

None

(0°C to +70°C)

NOTE: 1. Supports PC2100 modules with 2.5-3-3 timing

2. Supports PC1600 modules with 2-2-2 timing,

PRELIMINARY‡

1Gb: x4, x8, x16

DDR SDRAM

MT46V256M4 – 64 MEG X 4 X 4 BANKS

MT46V128M8 – 32 MEG X 8 X 4 BANKS

MT46V64M16 – 16 MEG X 16 X 4 BANKS

For the latest data sheet revisions, please refer to the

Micron Web site: www.micron.com/datasheets

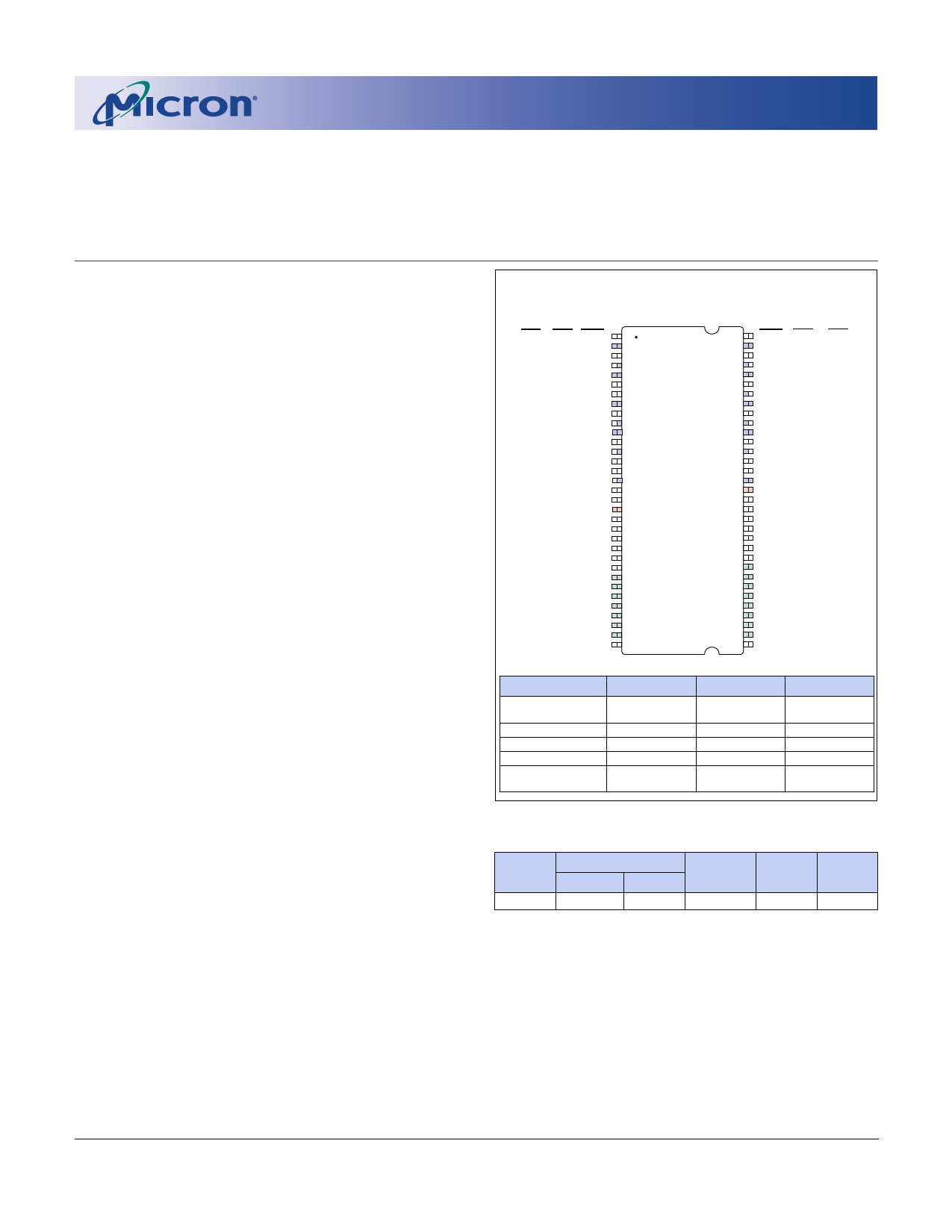

Figure 1: Pin Assignment (Top View)

66-pin TSOP

x4

x8

x16

VDD

VDD

VDD

1

NC DQ0 DQ0

2

VDDQ VDDQ VDDQ

3

NC

NC DQ1

4

DQ0 DQ1 DQ2

5

VSSQ VSSQ VssQ

6

NC

NC DQ3

7

NC DQ2 DQ4

8

VDDQ VDDQ VDDQ

9

NC

NC DQ5

10

DQ1 DQ3 DQ6

11

VSSQ VSSQ VssQ

12

NC

NC DQ7

13

NC

NC

NC

14

VDDQ VDDQ VDDQ

15

NC

NC LDQS

16

A13 A13 A13

17

VDD

VDD

VDD

18

DNU DNU DNU

19

NC

NC LDM

20

WE# WE# WE#

21

CAS# CAS# CAS#

22

RAS# RAS# RAS#

23

CS# CS# CS#

24

NC

NC

NC

25

BA0 BA0 BA0

26

BA1 BA1 BA1

27

A10/AP A10/AP A10/AP

28

A0

A0

A0

29

A1

A1

A1

30

A2

A2

A2

31

A3

A3

A3

32

VDD

VDD

VDD

33

x16

x8

x4

66

VSS

VSS

VSS

65

DQ15 DQ7 NC

64

VSSQ VSSQ VSSQ

63

DQ14 NC

NC

62

DQ13 DQ6 DQ3

61

VDDQ VDDQ VDDQ

60

DQ12 NC

NC

59

DQ11 DQ5 NC

58

VSSQ VSSQ VSSQ

57

DQ10 NC

NC

56

DQ9 DQ4 DQ2

55

VDDQ VDDQ VDDQ

54

DQ8 NC

NC

53

NC

NC

NC

52

VSSQ VSSQ VSSQ

51

UDQS DQS DQS

50

DNU DNU DNU

49

VREF

VREF

VREF

48

VSS

VSS

VSS

47

UDM DM DM

46

CK# CK# CK#

45

CK

CK

CK

44

CKE CKE CKE

43

NC

NC

NC

42

A12 A12 A12

41

A11 A11 A11

40

A9

A9

A9

39

A8

A8

A8

38

A7

A7

A7

37

A6

A6

A6

36

A5

A5

A5

35

A4

A4

A4

34

VSS

VSS

VSS

256 MEG X 4 128 MEG X 8 64 MEG X 16

Configuration

Refresh Count

Row Addressing

Bank Addressing

Column Addressing

64 Meg x 4 x 4

banks

8K

16K (A0–A13)

4(BA0,BA1)

4K(A0–A9,

A11, A12)

32 Meg x 8 x 4

banks

8K

16K (A0–A13)

4(BA0,BA1)

2K(A0–A9, A11)

16 Meg x 16 x 4

banks

8K

16K (A0–A13)

4(BA0,BA1)

1K(A0–A9)

Key Timing Parameters

SPEED

GRADE

-75

CLOCKRATE

CL=2** CL=2.5**

100 MHz 133MHz

DATA-OUT

WINDOW*

2.5ns

ACCESS

WINDOW

±0.75ns

DQS–DQ

SKEW

+0.5ns

* Minimum clock rate @ CL= 2.5

** CL = CAS (Read) Latency

09005aef8076894f

1gbBDDRx4x8x16_1.fm - Rev. A 3/03 EN

1

©2003 Micron Technology, Inc.

‡PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE FOR EVALUATION AND REFERENCE PURPOSES ONLY AND ARE SUBJECT TO CHANGE BY

MICRON WITHOUT NOTICE. PRODUCTS ARE ONLY WARRANTED BY MICRON TO MEET MICRON’S PRODUCTION DATA SHEET SPECIFICATIONS.