MT8888 データシートの表示(PDF) - Mitel Networks

部品番号

コンポーネント説明

メーカー

MT8888 Datasheet PDF : 16 Pages

| |||

Functional Description

The MT8888C/MT8888C-1 Integrated DTMF

Transceiver consists of a high performance DTMF

receiver with an internal gain setting amplifier and a

DTMF generator which employs a burst counter to

synthesize precise tone bursts and pauses. A call

progress mode can be selected so that frequencies

within the specified passband can be detected. The

Intel micro interface allows microcontrollers, such as

the 8080, 80C31/51 and 8085, to access the

MT8888C/MT8888C-1 internal registers.

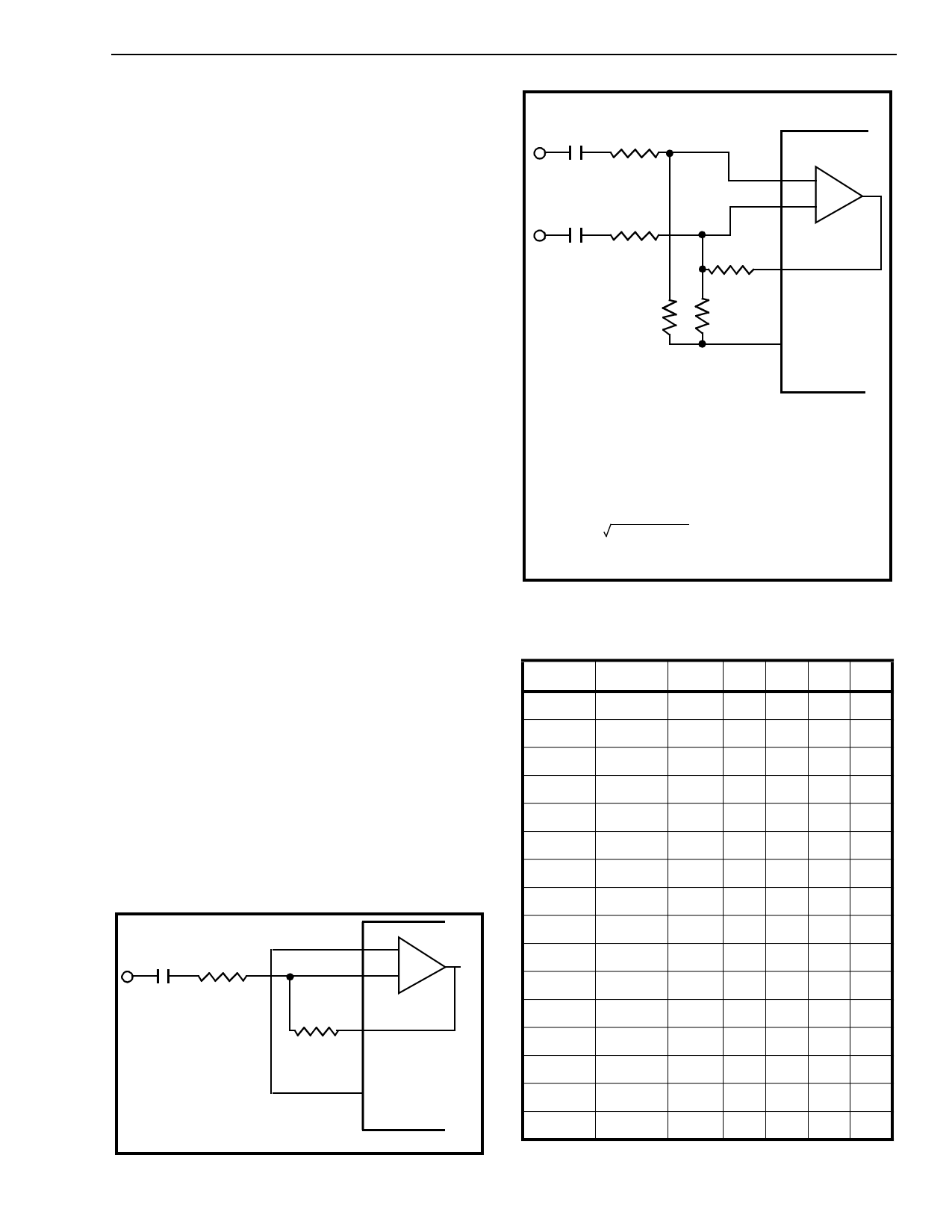

Input Configuration

The input arrangement of the MT8888C/MT8888C-1

provides a differential-input operational amplifier as

well as a bias source (VRef), which is used to bias the

inputs at VDD/2. Provision is made for connection of

a feedback resistor to the op-amp output (GS) for

gain adjustment. In a single-ended configuration, the

input pins are connected as shown in Figure 3.

Figure 4 shows the necessary connections for a

differential input configuration.

Receiver Section

Separation of the low and high group tones is

achieved by applying the DTMF signal to the inputs

of two sixth-order switched capacitor bandpass

filters, the bandwidths of which correspond to the low

and high group frequencies (see Table 1). These

filters incorporate notches at 350 Hz and 440 Hz for

exceptional dial tone rejection. Each filter output is

followed by a single order switched capacitor filter

section, which smooths the signals prior to limiting.

Limiting is performed by high-gain comparators

which are provided with hysteresis to prevent

detection of unwanted low-level signals. The outputs

of the comparators provide full rail logic swings at

the frequencies of the incoming DTMF signals.

IN+

IN-

C

RIN

RF

GS

VOLTAGE GAIN

(AV) = RF / RIN

VRef

MT8888C/

MT8888C-1

Figure 3 - Single-Ended Input Configuration

MT8888C/MT8888C-1

C1 R1

C2 R4

R5

R3

R2

DIFFERENTIAL INPUT AMPLIFIER

C1 = C2 = 10 nF

R1 = R4 = R5 = 100 kΩ

R2 = 60kΩ, R3 = 37.5 kΩ

R3 = (R2R5)/(R2 + R5)

VOLTAGE GAIN

(AV diff) - R5/R1

INPUT IMPEDANCE

(ZINdiff) = 2 R12 + (1/ωC)2

IN+

IN-

GS

VRef

MT8888C/

MT8888C-1

Figure 4 - Differential Input Configuration

FLOW

FHIGH

DIGIT D3

D2

D1

D0

697 1209

1

0001

697 1336

2

0010

697 1477

3

0011

770 1209

4

0100

770 1336

5

0101

770 1477

6

0110

852 1209

7

0111

852 1336

8

1000

852 1477

9

1001

941 1336

0

1010

941 1209

*

1011

941 1477

#

1100

697 1633

A

1101

770 1633

B

1110

852 1633

C 1111

941 1633

D 0000

0= LOGIC LOW, 1= LOGIC HIGH

Table 1. Functional Encode/Decode Table

4-93