MT90810 データシートの表示(PDF) - Mitel Networks

部品番号

コンポーネント説明

メーカー

MT90810 Datasheet PDF : 34 Pages

| |||

Preliminary Information

MT90810

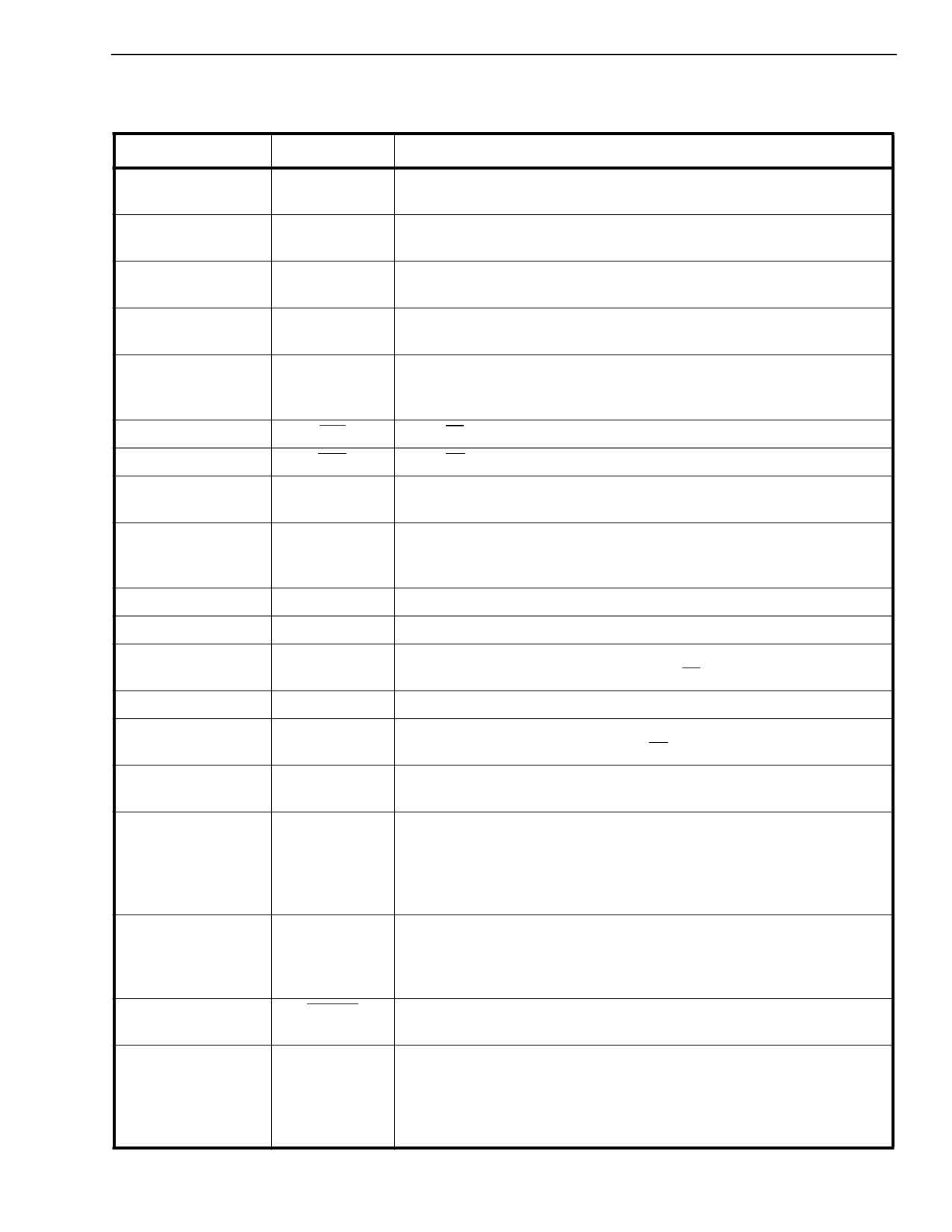

Pin Description

Pin #

58, 60, 63, 67, 70,

72, 74, 77

59, 61, 64, 68, 71,

73, 75, 78

80, 82, 83, 85

87, 88, 89, 90

4

55

56

54

53

91

92

94

95

97

98

100, 1, 2, 3, 5, 20,

33, 46, 57, 69, 81,

96

6, 7, 8, 9, 14, 28,

39, 51, 62, 76, 84,

99

19

35, 36, 37, 38, 42,

43, 44, 45

Name

DSo[0:7]

DSi[0:7]

LDO[0:3]

LDI[0:3]

CSTo

F0b

C4b

C2o

SEC8K

EX_8KA

EX_8KB

FRAME

CLK8

CLK4

CLK2

FGA[0:11]

FGB[0:11]

RESET

AD[0:7]

Description

MVIP DSo Streams (Bidirectional CMOS). 2.048Mb/s serial data

streams conforming to ST-BUS serial data stream specifications.

MVIP DSi Streams (Bidirectional CMOS). 2.048Mb/s serial data

streams conforming to ST-BUS serial data stream specifications.

Local Output Serial Streams (Output). Serial data streams

programmable to 2.048, 4.096 or 8.192Mb/s data rates.

Local Input Serial Streams (TTL Input). Serial data streams

programmable to 2.048, 4.096 or 8.192 Mb/s data rates.

Control ST-BUS Output (Output). This is a 1.024Mb/s output. The

state of each bit in this stream is determined by the CSTo bit in

connection memory high.

MVIP F0 signal (CMOS Input/Output). ST-BUS 8kHz framing signal

MVIP C4 signal (CMOS Input/Output). ST-BUS 4.096MHz clock

MVIP C2 signal (Output). ST-BUS 2.048MHz clock. This pin is

automatically set to high impedance when it is not driven.

MVIP SEC8K signal (CMOS Input/Output). A secondary 8kHz signal

used either as an input source to the on-chip digital PLL or as an

output to the MVIP bus.

External 8kHz input A (TTL Input).

External 8kHz input B (TTL Input).

Local Frame Output Signal (Output). This 8kHz framing signal has a

duty cycle and period equal to the MVIP F0 signal.

8MHz Local Output Clock (Output). This is a 8MHz clock.

4MHz Local Output Clock (Output). This 4MHz clock has a duty

cycle and period equal to the MVIP C4 signal.

2MHz Local Output Clock (Output). This 2MHz clock has a duty

cycle and period equal to the MVIP C2 signal.

Frame Group A framing signals (Output). Programmable framing

signals. The frame group outputs are determined by mode bits in the

frame register to be either programmed outputs, output drive enables

for DSo, or output framing pulses for use with local serial data

streams.

Frame Group B framing signals (Output). Programmable framing

signals. The frame group outputs are determined by mode bits in the

frame register to be either programmed outputs, output drive enables

for DSi, or output framing pulses for use with local serial data streams.

Chip Reset (Schmitt Input). This active low reset clears all internal

registers, connection memory and data memory

Microprocessor Address/Data Bus (Bidirectional TTL).

Microprocessor access to internal registers, connection and data

memories.

In non-multiplexed mode: data bus.

In multiplexed mode: multiplexed address and data bus.

2-147