CY7C4231-25JC データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CY7C4231-25JC Datasheet PDF : 21 Pages

| |||

CY7C4421/4201/4211/4221

CY7C4231/4241/4251

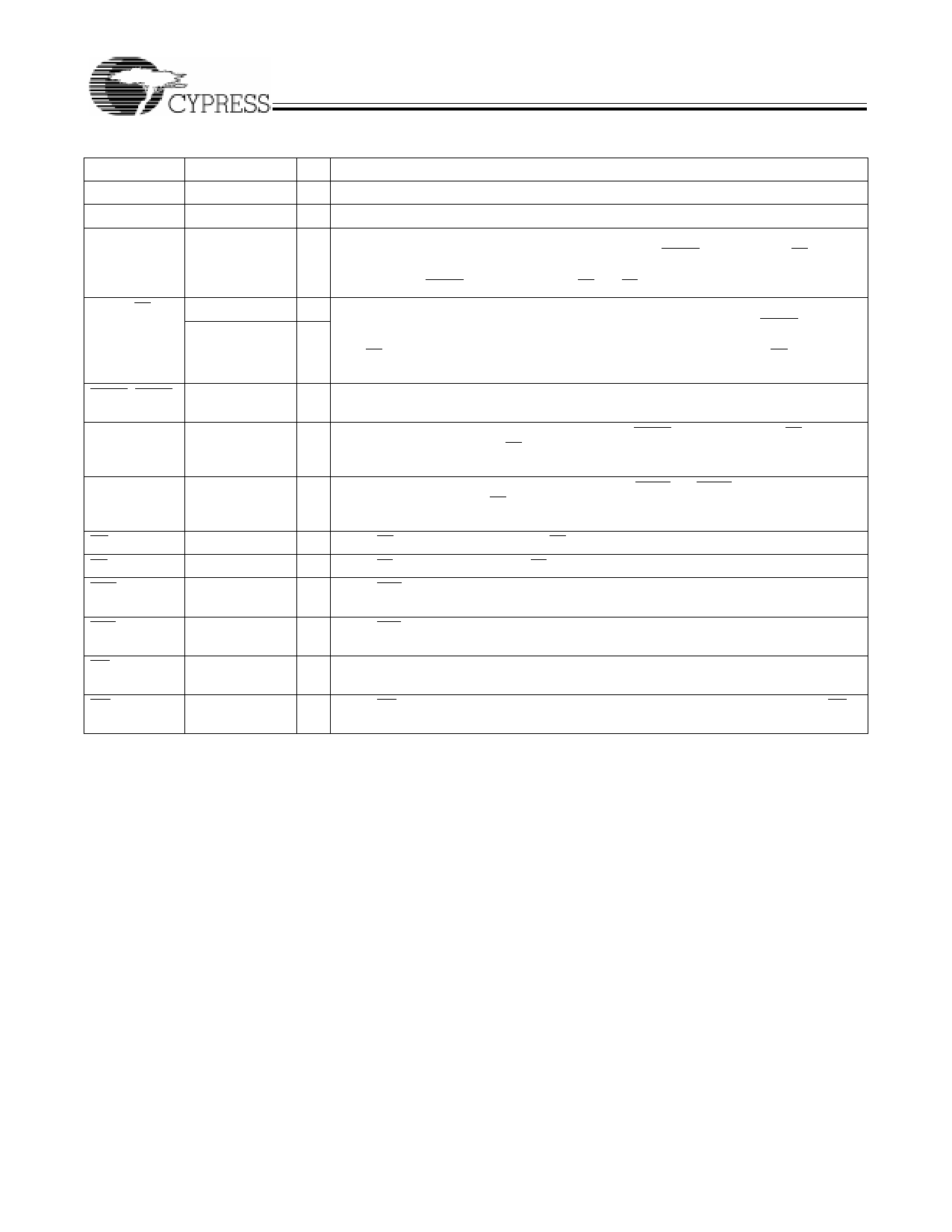

Pin Definitions

Signal Name Description

D0–8

Q0–8

WEN1

Data Inputs

Data Outputs

Write Enable 1

WEN2/LD

Write Enable 2

Dual Mode Pin Load

REN1, REN2

WCLK

Read Enable

Inputs

Write Clock

RCLK

Read Clock

EF

Empty Flag

FF

Full Flag

PAE

Programmable

Almost Empty

PAF

Programmable

Almost Full

RS

Reset

OE

Output Enable

I/O

Description

I Data Inputs for 9-bit bus

O Data Outputs for 9-bit bus

I The only write enable when device is configured to have programmable flags. Data is

written on a LOW-to-HIGH transition of WCLK when WEN1 is asserted and FF is HIGH.

If the FIFO is configured to have two write enables, data is written on a LOW-to-HIGH transition

of WCLK when WEN1 is LOW and WEN2/LD and FF are HIGH.

I If HIGH at reset, this pin operates as a second write enable. If LOW at reset, this pin

I

operates as a control to write or read the programmable flag offsets. WEN1 must be

LOW and WEN2 must be HIGH to write data into the FIFO. Data will not be written into the FIFO

if the FF is LOW. If the FIFO is configured to have programmable flags, WEN2/LD is held LOW

to write or read the programmable flag offsets.

I Enables the device for Read operation.

I The rising edge clocks data into the FIFO when WEN1 is LOW and WEN2/LD is HIGH

and the FIFO is not Full. When LD is asserted, WCLK writes data into the programmable flag-off-

set register.

I The rising edge clocks data out of the FIFO when REN1 and REN2 are LOW and the FIFO

is not Empty. When WEN2/LD is LOW, RCLK reads data out of the programmable flag-offset

register.

O When EF is LOW, the FIFO is empty. EF is synchronized to RCLK.

O When FF is LOW, the FIFO is full. FF is synchronized to WCLK.

O When PAE is LOW, the FIFO is almost empty based on the almost empty offset value pro-

grammed into the FIFO.

O When PAF is LOW, the FIFO is almost full based on the almost full offset value programmed

into the FIFO.

I Resets device to empty condition. A reset is required before an initial read or write

operation after power-up.

I When OE is LOW, the FIFO’s data outputs drive the bus to which they are connected. If OE is

HIGH, the FIFO’s outputs are in High Z (high-impedance) state.

3