SN74LS165D データシートの表示(PDF) - Motorola => Freescale

部品番号

コンポーネント説明

メーカー

SN74LS165D Datasheet PDF : 6 Pages

| |||

SN54 / 74LS165

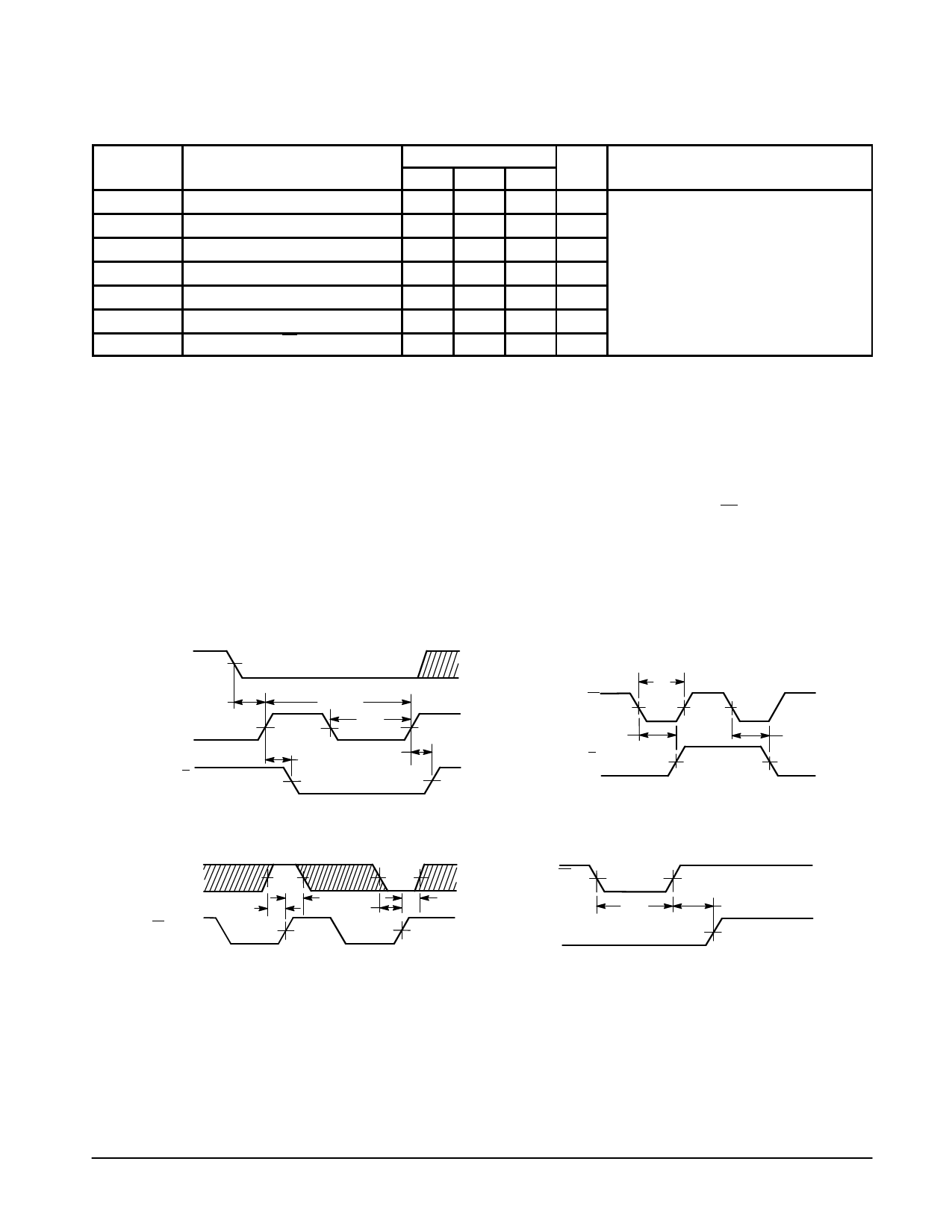

AC SETUP REQUIREMENTS (TA = 25°C)

Limits

Symbol

Parameter

Min Typ Max Unit

tW

CP Clock Pulse Width

25

ns

tW

PL Pulse Width

15

ns

ts

Parallel Data Setup Time

10

ns

ts

Serial Data Setup Time

20

ns

ts

CP1 to CP2 Setup Time1

30

ns

th

Hold Time

0

ns

trec

Recovery Time, PL to CP

45

ns

1 The role of CP1, and CP2 in an application may be interchanged.

Test Conditions

VCC = 5.0 V

DEFINITION OF TERMS:

SETUP TIME (ts) — is defined as the minimum time required

for the correct logic level to be present at the logic input prior

to the clock transition from LOW-to-HIGH in order to be recog-

nized and transferred to the outputs.

HOLD TIME (th) — is defined as the minimum time following

the clock transition from LOW-to-HIGH that the logic level

must be maintained at the input in order to ensure continued

recognition. A negative hold time indicates that the correct

logic level may be released prior to the clock transition from

LOW-to-HIGH and still be recognized.

RECOVERY TIME (trec) — is defined as the minimum time

required between the end of the PL pulse and the clock

transition from LOW-to-HIGH in order to recognize and

transfer loaded Data to the Q outputs.

AC WAVEFORMS

CP1

CP2

ts

1.3 V

Q7 OR Q7

1/fmax

tW

1.3 V

tPHL

1.3 V

tPLH

1.3 V

Figure 1

PL

1.3 V

tPLH

Q7 OR Q7

tW

1.3 V

1.3 V

1.3 V

tPHL

1.3 V

Figure 2

Pn

PL OR CP

ts(H)

1.3 V

th(H)

ts(L)

1.3 V

1.3 V

th(L)

1.3 V

Figure 3

PL

CP

1.3 V

tW

1.3 V

1.3 V

trec

Figure 4

FAST AND LS TTL DATA

5-293