PSD813F1-A データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

PSD813F1-A Datasheet PDF : 120 Pages

| |||

PSD813F1-A

5.0

PSD813F1

Architectural

Overview

6

Preliminary

PSD813F1 devices contain several major functional blocks. Figure 1 on page 3 shows the

architecture of the PSD813F1 device. The functions of each block are described briefly in

the following sections. Many of the blocks perform multiple functions and are user config-

urable.

5.1 Memory

The PSD813F1 contains the following memories:

• A 1 Mbit Flash

• A secondary 256 Kbit EEPROM memory

• A 16 Kbit SRAM.

Each of the memories is briefly discussed in the following paragraphs. A more detailed

discussion can be found in section 9.

The 1 Mbit Flash is the main memory of the PSD813F1. It is divided into eight equally-sized

sectors that are individually selectable.

The 256 Kbit EEPROM or Flash is divided into four equally-sized sectors. Each sector is

individually selectable.

The 16 Kbit SRAM is intended for use as a scratchpad memory or as an extension to the

microcontroller SRAM. If an external battery is connected to the PSD813F1’s Vstby pin,

data will be retained in the event of a power failure.

Each block of memory can be located in a different address space as defined by the user.

The access times for all memory types includes the address latching and DPLD decoding

time.

5.2 Page Register

The eight-bit Page Register expands the address range of the microcontroller by up to

256 times.The paged address can be used as part of the address space to access external

memory and peripherals or internal memory and I/O. The Page Register can also be used

to change the address mapping of blocks of Flash memory into different memory spaces for

in-circuit reprogramming.

5.3 PLDs

The device contains two PLD blocks, each optimized for a different function, as shown in

Table 2. The functional partitioning of the PLDs reduces power consumption, optimizes

cost/performance, and eases design entry.

The Decode PLD (DPLD) is used to decode addresses and generate chip selects for the

PSD813F1 internal memory and registers. The CPLD can implement user-defined logic

functions. The DPLD has combinatorial outputs. The CPLD has 16 Output Micro⇔Cells

and 3 combinatorial outputs. The PSD813F1 also has 24 Input Micro⇔Cells that can be

configured as inputs to the PLDs. The PLDs receive their inputs from the PLD Input Bus

and are differentiated by their output destinations, number of Product Terms, and

Micro⇔Cells.

The PLDs consume minimal power by using Zero-Power design techniques. The speed

and power consumption of the PLD is controlled by the Turbo Bit (ZPSD only) in the

PMMR0 register and other bits in the PMMR2 registers. These registers are set by the

microcontroller at runtime. There is a slight penalty to PLD propagation time when invoking

the ZPSD features.

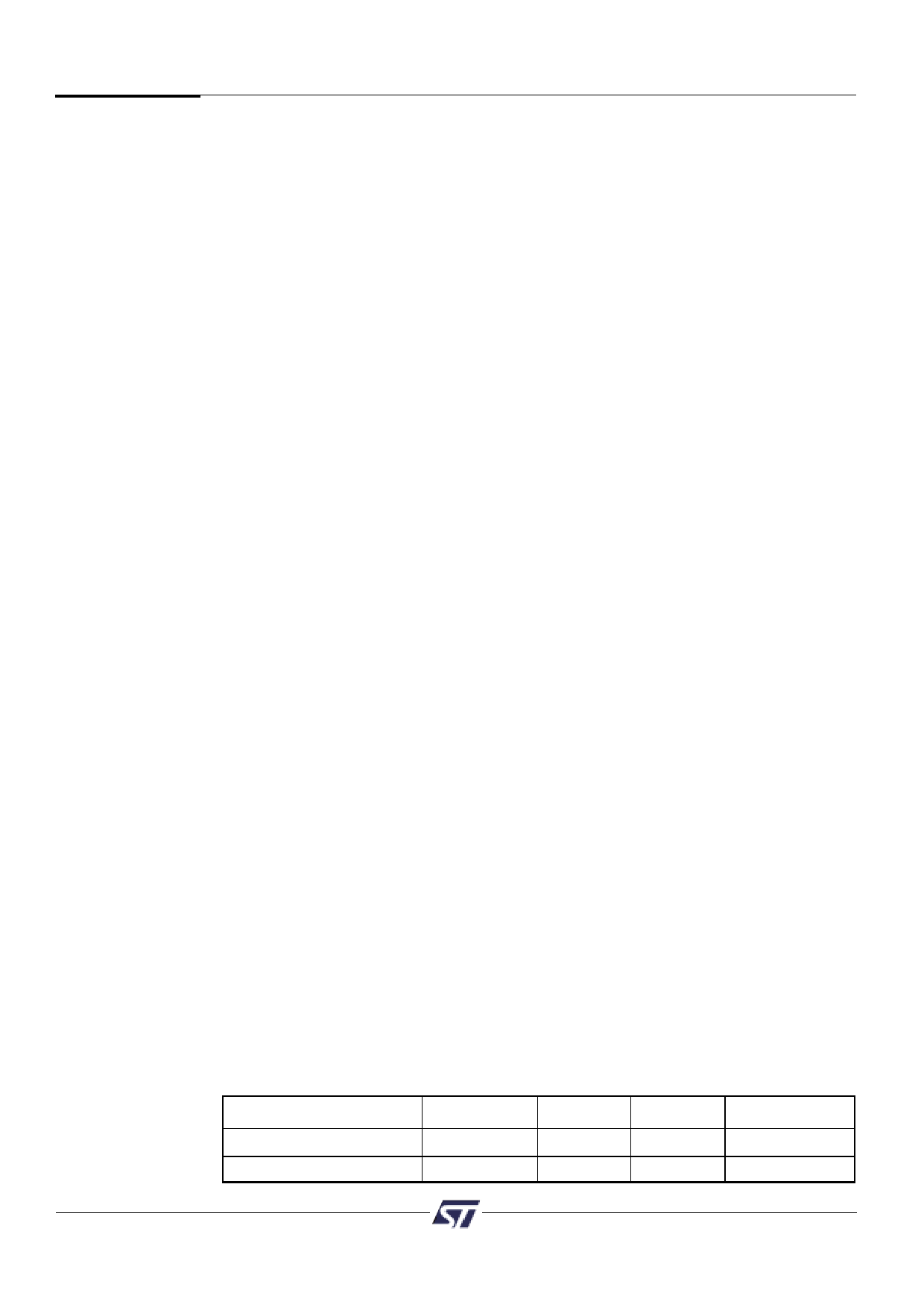

Table 2. PLD I/O Table

Name

Decode PLD

Complex PLD

Abbreviation

DPLD

CPLD

Inputs

73

73

Outputs

17

19

Product Terms

42

140