PZ3064 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

メーカー

PZ3064 Datasheet PDF : 20 Pages

| |||

Philips Semiconductors

64 macrocell CPLD

Product specification

PZ3064

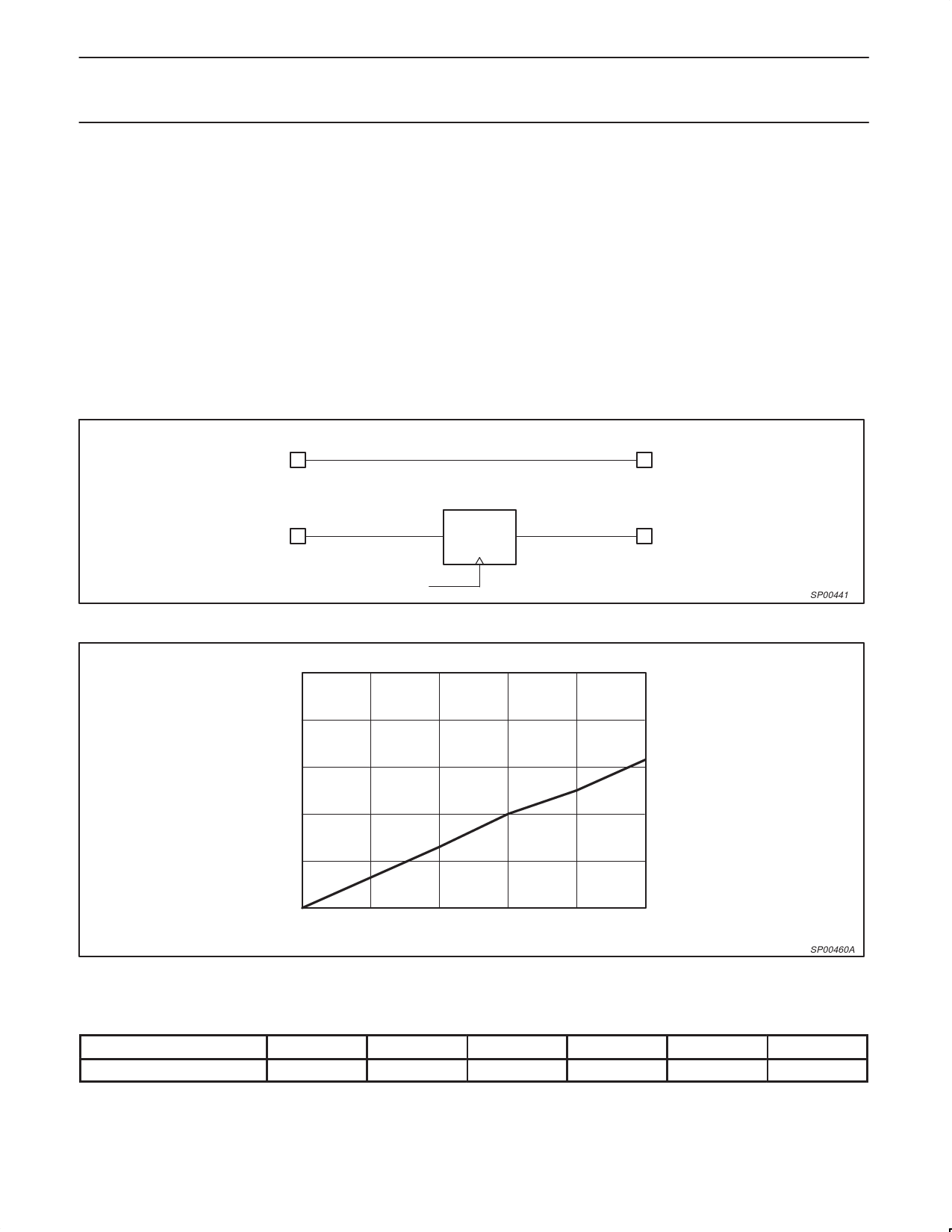

Simple Timing Model

Figure 4 shows the CoolRunner™ Timing Model. The CoolRunner™

timing model looks very much like a 22V10 timing model in that

there are three main timing parameters, including tPD, tSU, and tCO.

In other competing architectures, the user may be able to fit the

design into the CPLD, but is not sure whether system timing

requirements can be met until after the design has been fit into the

device. This is because the timing models of competing

architectures are very complex and include such things as timing

dependencies on the number of parallel expanders borrowed,

sharable expanders, varying number of X and Y routing channels

used, etc. In the XPLA™ architecture, the user knows up front

whether the design will meet system timing requirements. This is

due to the simplicity of the timing model. For example, in the

PZ3064 device, the user knows up front that if a given output uses

5 product terms or less, the tPD = 10ns, the tSU_PAL = 6ns, and the

tCO = 7ns. If an output is using 6 to 37 product terms, an additional

2ns must be added to the tPD and tSU timing parameters to account

for the time to propagate through the PLA array.

TotalCMOS™ Design Technique

for Fast Zero Power

Philips is the first to offer a TotalCMOS™ CPLD, both in process

technology and design technique. Philips employs a cascade of

CMOS gates to implement its Sum of Products instead of the

traditional sense amp approach. This CMOS gate implementation

allows Philips to offer CPLDs which are both high performance and

low power, breaking the paradigm that to have low power, you must

have low performance. Refer to Figure 5 and Table 2 showing the IDD

vs. Frequency of our PZ3064 TotalCMOS™ CPLD.

INPUT PIN

tPD_PAL = COMBINATORIAL PAL ONLY

tPD_PLA = COMBINATORIAL PAL + PLA

OUTPUT PIN

INPUT PIN

REGISTERED

tSU_PAL = PAL ONLY

tSU_PLA = PAL + PLA

D

REGISTERED

Q

tCO

OUTPUT PIN

CLOCK

Figure 4. CoolRunner™ Timing Model

SP00441

100

80

IDD

(mA)

60

TYPICAL

40

20

0

0

20

40

60

80

100

FREQUENCY (MHz)

Figure 5. IDD vs. Frequency @ VDD = 3.3V, 25°C

Table 2. IDD vs. Frequency

VDD = 3.3V

FREQUENCY (MHz)

0

20

40

60

80

Typical IDD ( mA)

0.04

13

26

40

50

SP00460A

100

63

1997 Mar 05

86