STK1743-D35I データシートの表示(PDF) - Simtek Corporation

部品番号

コンポーネント説明

メーカー

STK1743-D35I Datasheet PDF : 10 Pages

| |||

STK1743

STK1743 clock registers before reading clock data

to prevent reading of data in transition. Stopping the

internal register updates does not affect clock accu-

racy.

The updating process is stopped by writing a “1” to

the read bit (the seventh most significant bit in the

control register), and will not restart until a “0” is

written to the read bit. The RTC registers can then

be read while the internal clock continues to run.

Within one second after a “0” is written to the read

bit, all STK1743 registers are simultaneously

updated.

SRAM WRITE AND

SETTING THE CLOCK

A WRITE cycle is performed whenever E and W are

low. The address inputs must be stable prior to

entering the WRITE cycle and must remain stable

until either E or W goes high at the end of the cycle.

The data on the common I/O pins DQ0-7 will be writ-

ten into the memory if it is valid tDVWH before the end

of a W controlled WRITE or tDVEH before the end of

an E controlled WRITE.

It is recommended that G be kept high during the

entire WRITE cycle to avoid data bus contention on

the common I/O lines. If G is left low, internal cir-

cuitry will turn off the output buffers tWLQZ after W

goes low.

Setting the write bit (the eighth most significant bit

of the control register) to a “1” halts updates to the

STK1743 registers. The correct day, date and time

can then be written into the registers in 24-hour

BCD format. Resetting the write bit to “0” transfers

those values to the actual clock counters, after

which the clock resumes normal operation.

CLOCK ACCURACY

The STK1743 is guaranteed to be accurate to

within ± 1 minute per month at 25°C. The part

requires no additional calibration, and temperature

variations will have a negligible effect in most appli-

cations.

DATA RETENTION MODE

During normal operation (VCC ≥ 4.5V), the STK1743

can be accessed with standard SRAM READ and

WRITE cycles. However, when VCC falls below the

power-fail voltage, VSWITCH (the voltage at which

write protection occurs), access to the internal clock

register and the SRAM is blocked. At this voltage,

SRAM data is automatically stored to the integral

EEPROM, and power for the clock oscillator

switches from the VCC pin to the internal capacitor.

The capacitor maintains clock activity and data until

VCC returns to its nominal level.

SOFTWARE NONVOLATILE STORE

The STK1743 software STORE cycle is initiated by

executing sequential READ cycles from six specific

address locations. During the STORE cycle an erase

of the previous nonvolatile data is first performed,

followed by a program of the nonvolatile elements.

The program operation copies the SRAM data into

nonvolatile memory. Once a STORE cycle is initi-

ated, further input and output are disabled until the

cycle is completed.

Because a sequence of READs from specific

addresses is used for STORE initiation, it is impor-

tant that no other READ or WRITE accesses inter-

vene in the sequence or the sequence will be

aborted and no STORE or RECALL will take place.

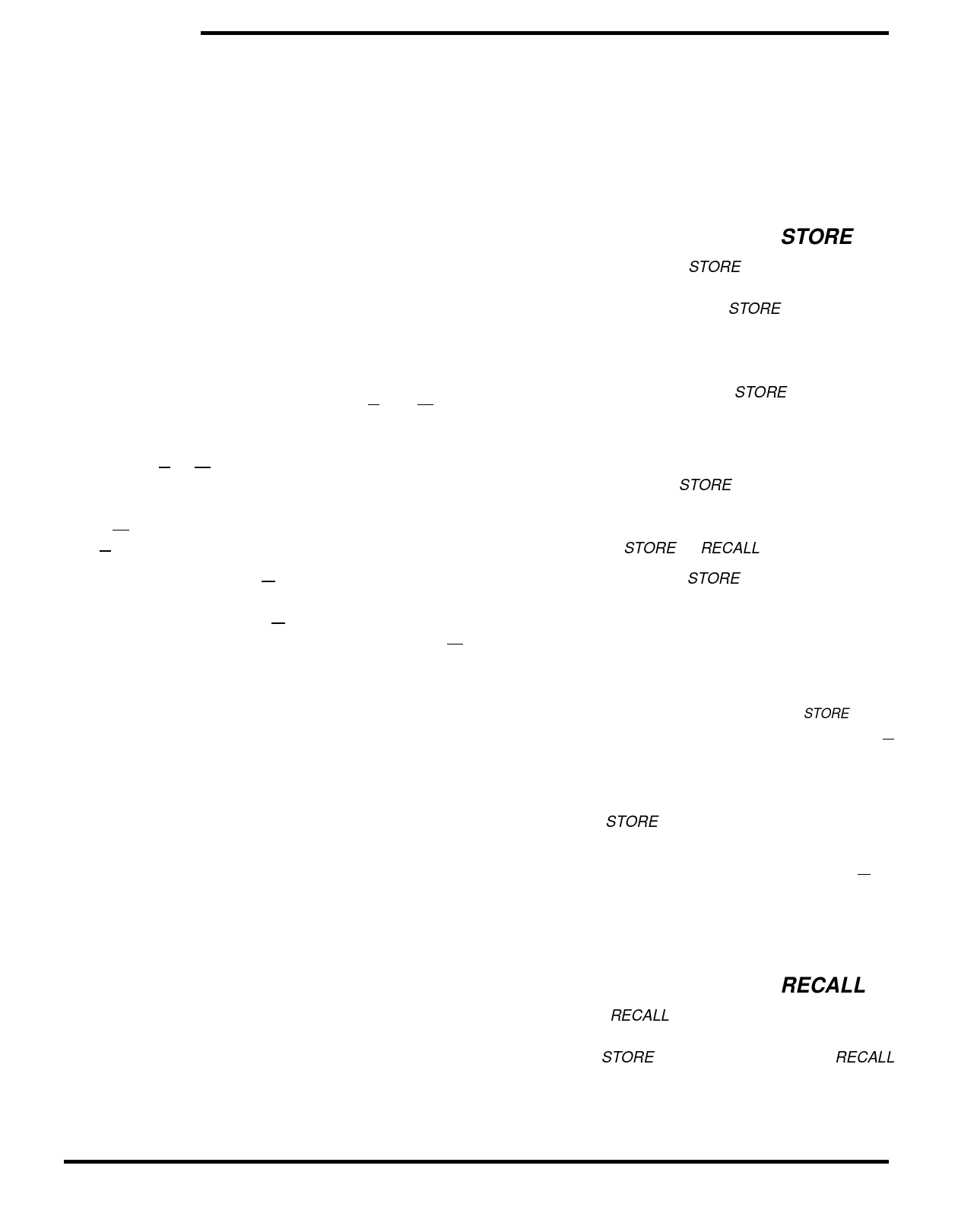

To initiate the software STORE cycle, the following

READ sequence must be performed:

1. Read address

2. Read address

3. Read address

4. Read address

5. Read address

6. Read address

0000 (hex)

1555 (hex)

0AAA (hex)

1FFF (hex)

10F0 (hex)

0F0F (hex)

Valid READ

Valid READ

Valid READ

Valid READ

Valid READ

Initiate STORE cycle

The software sequence must be clocked with E

controlled READs.

Once the sixth address in the sequence has been

entered, the STORE cycle will commence and the

memory accesses will be disabled. It is important

that READ cycles and not WRITE cycles be used in

the sequence, although it is not necessary that G be

low for the sequence to be valid. After the tSTORE

cycle time has been fulfilled, the SRAM will again be

activated for READ and WRITE operation.

SOFTWARE NONVOLATILE RECALL

A software RECALL cycle is initiated with a

sequence of READ operations in a manner similar to

the software STORE initiation. To initiate the RECALL

cycle, the following sequence of READ operations

must be performed:

March 1999

7-8