S3076TT データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

メーカー

S3076TT Datasheet PDF : 18 Pages

| |||

MULTI-RATE SONET/SDH CLOCK RECOVERY UNIT

S3076

FIBRE CHANNEL

JITTER CHARACTERISTICS

Performance

The S3076 PLL complies with the jitter specifications

proposed for Fibre Channel equipment defined by the

fibre channel methodology for Jitter specification.

Input Jitter Tolerance

Input jitter tolerance is defined as the peak to

peak amplitude of sinusoidal jitter applied on the

input signal that causes an equivalent 1 dB opti-

cal/electrical power penalty. Fibre Channel input

jitter tolerance requirements are shown in

Table 3.

Jitter Generation

The jitter of the serial clock and serial data outputs

shall not exceed the value specified in Table 4 when

a serial data input with no jitter is presented to the

serial data inputs.

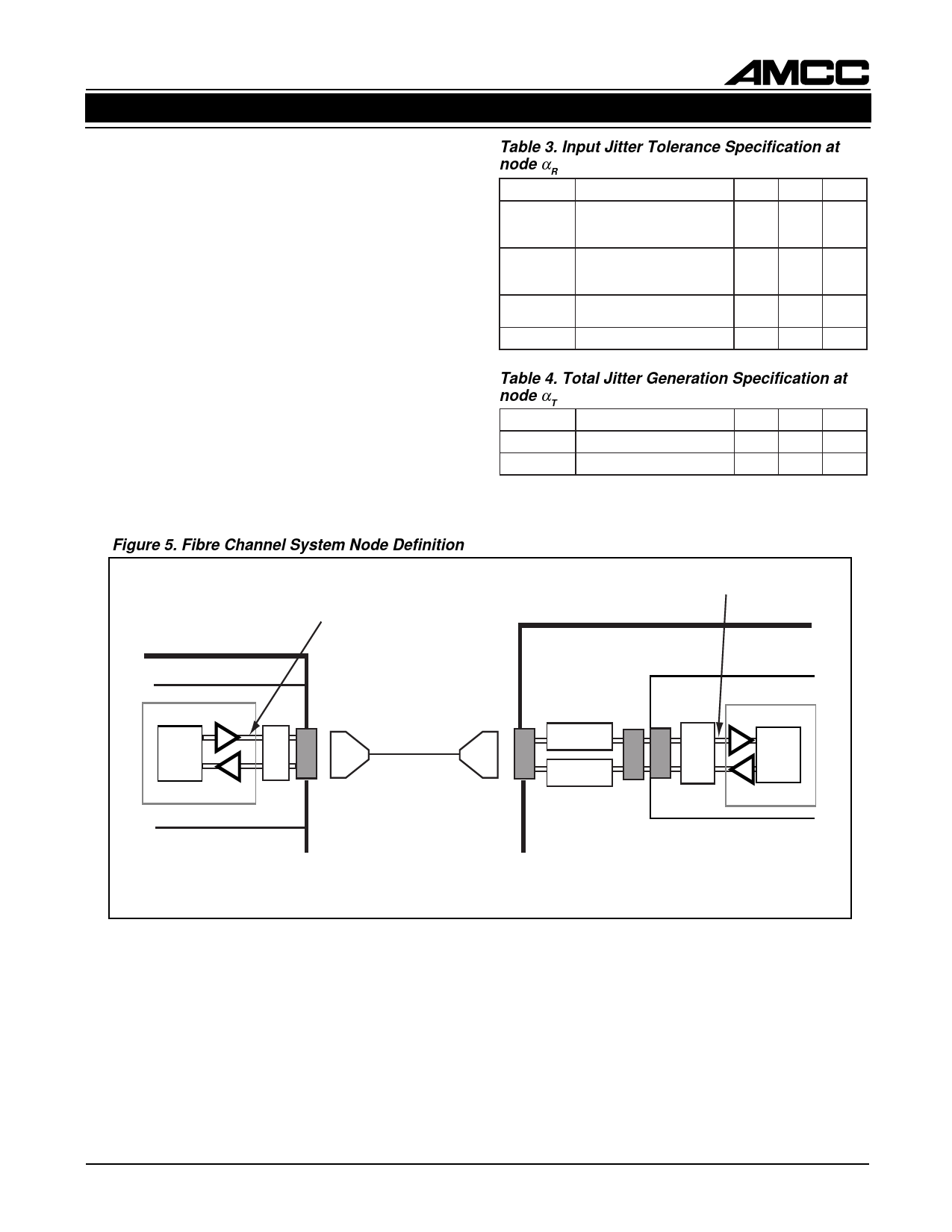

Figure 5. Fibre Channel System Node Definition

Table 3. Input Jitter Tolerance Specification at

node αR

Parameters

Description

Min Max Units

Frequency Dependent

t

Jitter Tolerance

0.10 – UI p-p

FDJ

(637 kHz to ≥ 5 MHz)

Deterministic Jitter

tDJ

Tolerance

0.38 – UI p-p

(637 kHz – 531 MHz)

tRJ

Random Jitter

(637 kHz – 531 MHz)

0.22 – UI p-p

tTJ

Total Jitter

0.70 – UI p-p

Table 4. Total Jitter Generation Specification at

node αT

Parameters

Description

Min Max Units

DJ

Deterministic Jitter

0.08 UI p-p

TJ

Total Jitter

0.23 UI p-p

SYSTEM

HOST ADAPTOR

SERDES

αT = Component Transmitter Node

Componet Receiver Node = αR

SYSTEM

STORAGE

DISK DRIVE

SERDES

BACKPLANE

PBC

REPEAETERS

CABLES

CONNECTORS

October 23, 2000 / Revision A

5