XC2000 データシートの表示(PDF) - Infineon Technologies

部品番号

コンポーネント説明

メーカー

XC2000 Datasheet PDF : 101 Pages

| |||

Preliminary

XC2267 / XC2264

XC2000 Family Derivatives

Electrical Parameters

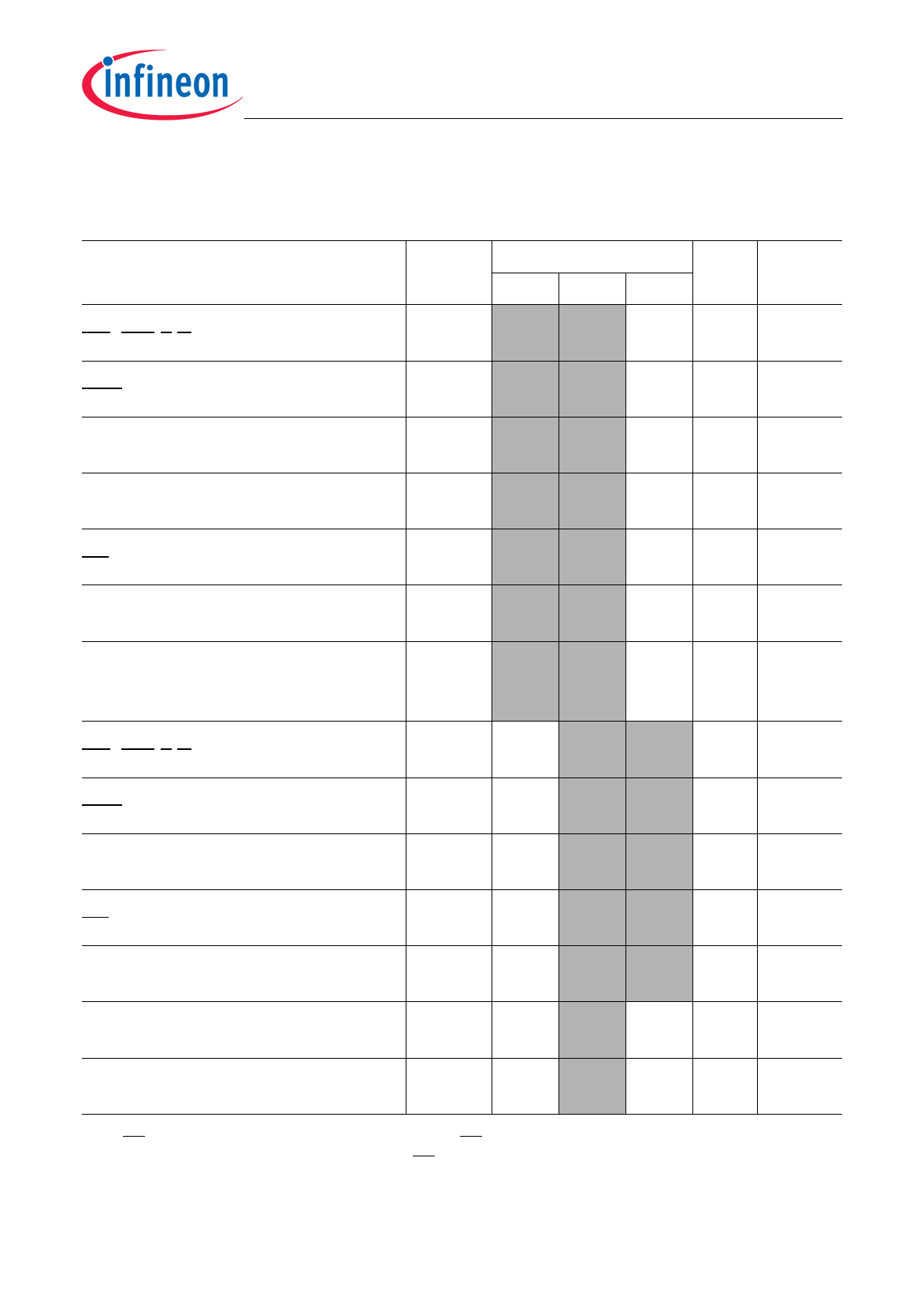

Table 22

External Bus Cycle Timing for 4.5 V ≤ VDDP ≤ 5.5 V

(Operating Conditions apply)

Parameter

Symbol

Limits

Unit Note

Min. Typ. Max.

Output valid delay for:

RD, WR(L/H)

tc10 CC –

13 ns

Output valid delay for:

BHE, ALE

tc11 CC –

13 ns

Output valid delay for:

tc12 CC –

A23 … A16, A15 … A0 (on P0/P1)

14 ns

Output valid delay for:

A15 … A0 (on P2/P10)

tc13 CC –

14 ns

Output valid delay for:

CS

tc14 CC –

13 ns

Output valid delay for:

tc15 CC –

D15 … D0 (write data, MUX-mode)

14 ns

Output valid delay for:

D15 … D0 (write data, DEMUX-

mode)

tc16 CC –

14 ns

Output hold time for:

RD, WR(L/H)

tc20 CC 0

8

ns

Output hold time for:

BHE, ALE

tc21 CC 0

8

ns

Output hold time for:

tc23 CC 0

A23 … A16, A15 … A0 (on P2/P10)

8

ns

Output hold time for:

CS

tc24 CC 0

8

ns

Output hold time for:

D15 … D0 (write data)

tc25 CC 0

8

ns

Input setup time for:

READY, D15 … D0 (read data)

tc30 SR 18

–

ns

Input hold time for:

READY, D15 … D0 (read data)1)

tc31 SR -4

–

ns

1) Read data are latched with the same (internal) clock edge that triggers the address change and the rising edge

of RD. Therefore address changes before the end of RD have no impact on (demultiplexed) read cycles. Read

data can be removed after the rising edge of RD.

Data Sheet

89

V0.1, 2007-02

Draft Version