SST34HF1621C データシートの表示(PDF) - Silicon Storage Technology

部品番号

コンポーネント説明

メーカー

SST34HF1621C Datasheet PDF : 38 Pages

| |||

16 Mbit Concurrent SuperFlash + 2/4 Mbit SRAM ComboMemory

SST34HF1621C / SST34HF1641C

Data Sheet

against inadvertent flash write, the SST34HF16x1C

devices contain on-chip hardware and software data pro-

tection schemes.

The flash and SRAM operate as two independent memory

banks with respective bank enable signals. The memory

bank selection is done by two bank enable signals. The

SRAM bank enable signals, BES1# and BES2, select the

SRAM bank. The flash memory bank enable signal, BEF#,

has to be used with Software Data Protection (SDP) com-

mand sequence when controlling the Erase and Program

operations in the flash memory bank. The memory banks

are superimposed in the same memory address space

where they share common address lines, data lines, WE#

and OE# which minimize power consumption and area.

Designed, manufactured, and tested for applications requir-

ing low power and small form factor, the SST34HF16x1C

are offered in extended temperatures and a small footprint

package to meet board space constraint requirements. See

Figures 4 and 5 for pin assignments.

Device Operation

The SST34HF16x1C uses BES1#, BES2 and BEF# to

control operation of either the flash or the SRAM memory

bank. When BEF# is low, the flash bank is activated for

Read, Program or Erase operation. When BES1# is low,

and BES2 is high the SRAM is activated for Read and

Write operation. BEF# and BES1# cannot be at low level,

and BES2 cannot be at high level at the same time. If all

bank enable signals are asserted, bus contention will

result and the device may suffer permanent damage.

All address, data, and control lines are shared by flash and

SRAM memory banks which minimizes power consump-

tion and loading. The device goes into standby when BEF#

and BES1# bank enables are raised to VIHC (Logic High) or

when BEF# is high and BES2 is low.

Concurrent Read/Write Operation

Dual bank architecture of SST34HF16x1C devices allows

the Concurrent Read/Write operation whereby the user

can read from one bank while programming or erasing in

the other bank. This operation can be used when the user

needs to read system code in one bank while updating

data in the other bank. See Figures 2 and 3 for dual-bank

memory organization.

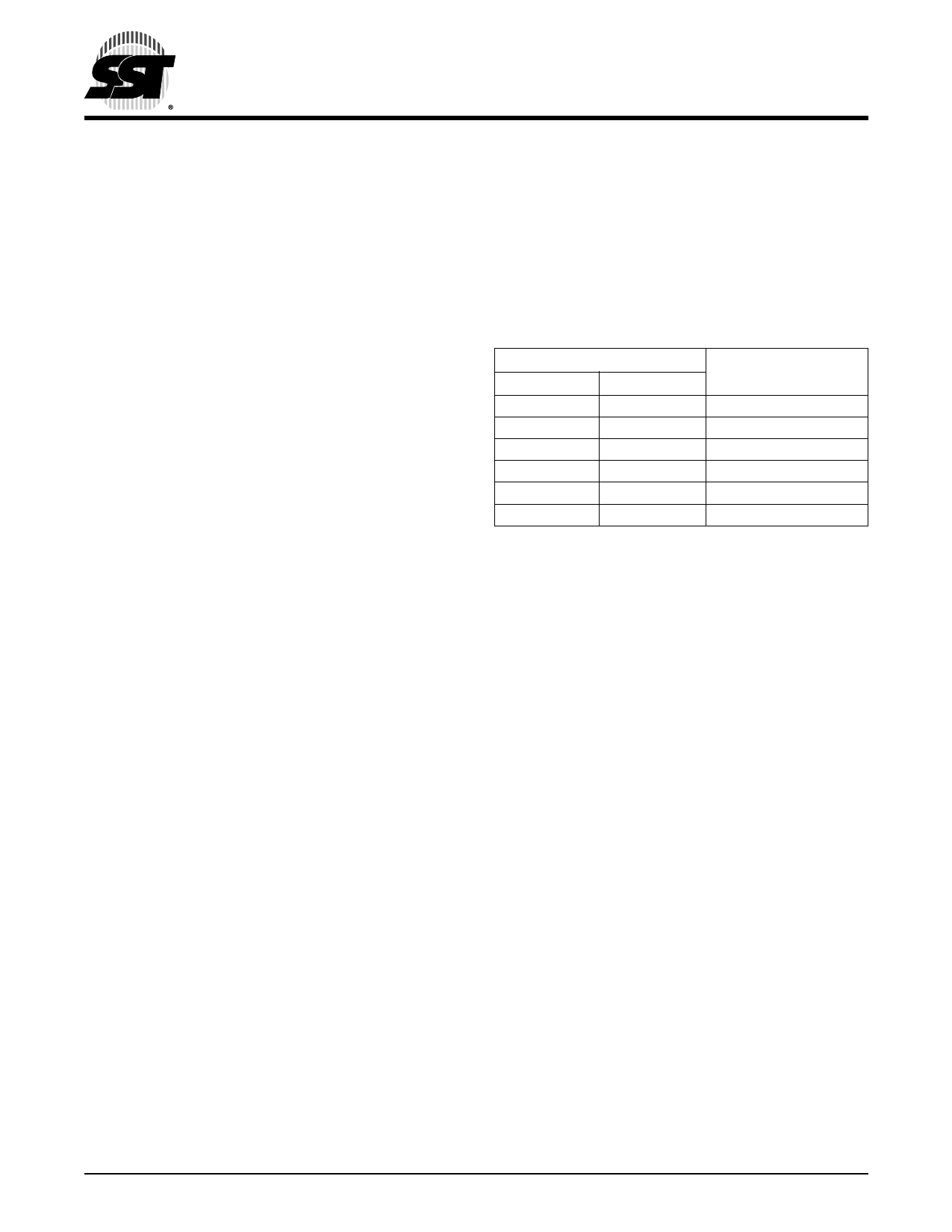

Concurrent Read/Write States

Flash

Bank 1

Read

Write

Write

No Operation

Write

No Operation

Bank 2

Write

Read

No Operation

Write

No Operation

Write

SRAM

No Operation

No Operation

Read

Read

Write

Write

Note: For the purposes of this table, Write means to perform

Block-/Sector-Erase or Program operations

as applicable to the appropriate bank.

Flash Read Operation

The Read operation of the SST34HF16x1C is controlled by

BEF# and OE#, both have to be low for the system to

obtain data from the outputs. BEF# is used for device

selection. When BEF# is high, the chip is deselected and

only standby power is consumed. OE# is the output control

and is used to gate data from the output pins. The data bus

is in high impedance state when either BEF# or OE# is

high. Refer to the Read cycle timing diagram for further

details (Figure 9).

©2006 Silicon Storage Technology, Inc.

2

S71252-03-000

8/06