SST49LF008A データシートの表示(PDF) - Silicon Storage Technology

部品番号

コンポーネント説明

メーカー

SST49LF008A Datasheet PDF : 42 Pages

| |||

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

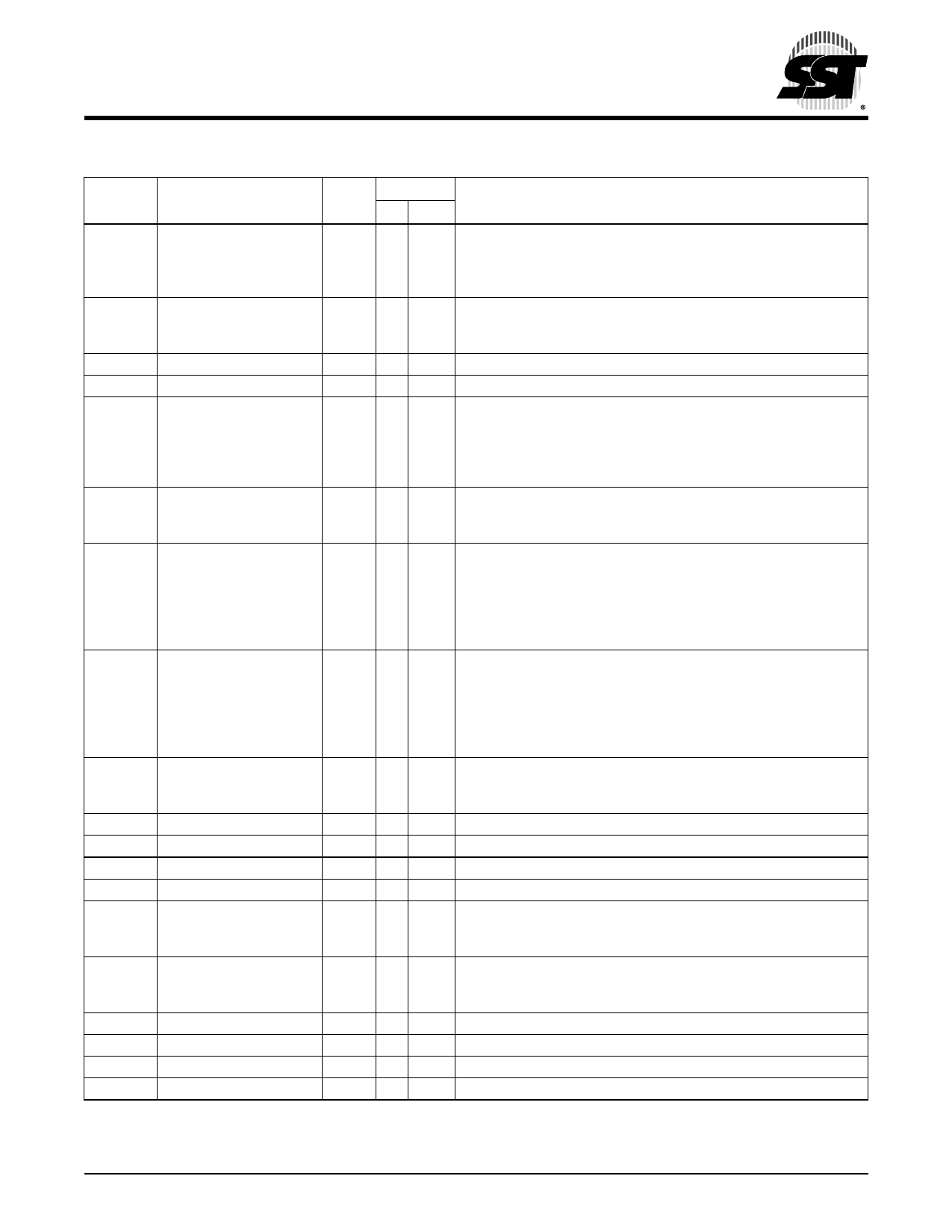

TABLE 1: Pin Description

Symbol Pin Name

A10-A0 Address

DQ7-DQ0 Data

OE#

WE#

IC

Output Enable

Write Enable

Interface

Configuration Pin

INIT#

Initialize

ID[3:0] Identification Inputs

FGPI[4:0] General Purpose Inputs

TBL#

Top Block Lock

FWH[3:0]

CLK

FWH4

RST#

WP#

FWH I/Os

Clock

FWH Input

Reset

Write Protect

R/C#

Row/Column Select

RES

VDD

VSS

NC

Reserved

Power Supply

Ground

No Connection

1. I = Input, O = Output

Type1

I

I/O

I

I

I

I

I

I

I

I/O

I

I

I

I

I

PWR

PWR

I

Interface

PP FWH

X

X

X

X

XX

X

X

X

X

X

X

X

XX

X

X

X

XX

XX

XX

Functions

Inputs for low-order addresses during Read and Write operations.

Addresses are internally latched during a Write cycle. For the pro-

gramming interface, these addresses are latched by R/C# and share

the same pins as the high-order address inputs.

To output data during Read cycles and receive input data during

Write cycles. Data is internally latched during a Write cycle. The out-

puts are in tri-state when OE# is high.

To gate the data output buffers

To control the Write operations

This pin determines which interface is operational. When held high,

programmer mode is enabled and when held low, FWH mode is

enabled. This pin must be setup at power-up or before return from

reset and not change during device operation. This pin is internally

pulled- down with a resistor between 20-100 KΩ.

This is the second reset pin for in-system use. This pin is internally

combined with the RST# pin; If this pin or RST# pin is driven low,

identical operation is exhibited.

These four pins are part of the mechanism that allows multiple parts

to be attached to the same bus. The strapping of these pins is used

to identify the component.The boot device must have ID[3:0]=0000

and it is recommended that all subsequent devices should use

sequential up-count strapping. These pins are internally pulled-down

with a resistor between 20-100 KΩ.

These individual inputs can be used for additional board flexibility.

The state of these pins can be read through GPI_REG register.

These inputs should be at their desired state before the start of the

PCI clock cycle during which the read is attempted, and should

remain in place until the end of the Read cycle. Unused GPI pins

must not be floated.

When low, prevents programming to the Boot Block sectors at top of

memory. When TBL# is high it disables hardware write protection for

the top block sectors. This pin cannot be left unconnected.

I/O Communications

To provide a clock input to the control unit

Input Communications

To reset the operation of the device

When low, prevents programming to all but the highest addressable

blocks. When WP# is high it disables hardware write protection for

these blocks. This pin cannot be left unconnected.

Select For the Programming interface, this pin determines whether

the address pins are pointing to the row addresses, or to the column

addresses.

These pins must be left unconnected.

To provide power supply (3.0-3.6V)

Circuit ground (OV reference) All VSS pins must be grounded.

Unconnected pins

T1.4 1161

©2006 Silicon Storage Technology, Inc.

9

S71161-11-000

3/06