ST18AU1_DS データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

ST18AU1_DS Datasheet PDF : 87 Pages

| |||

ST18-AU1

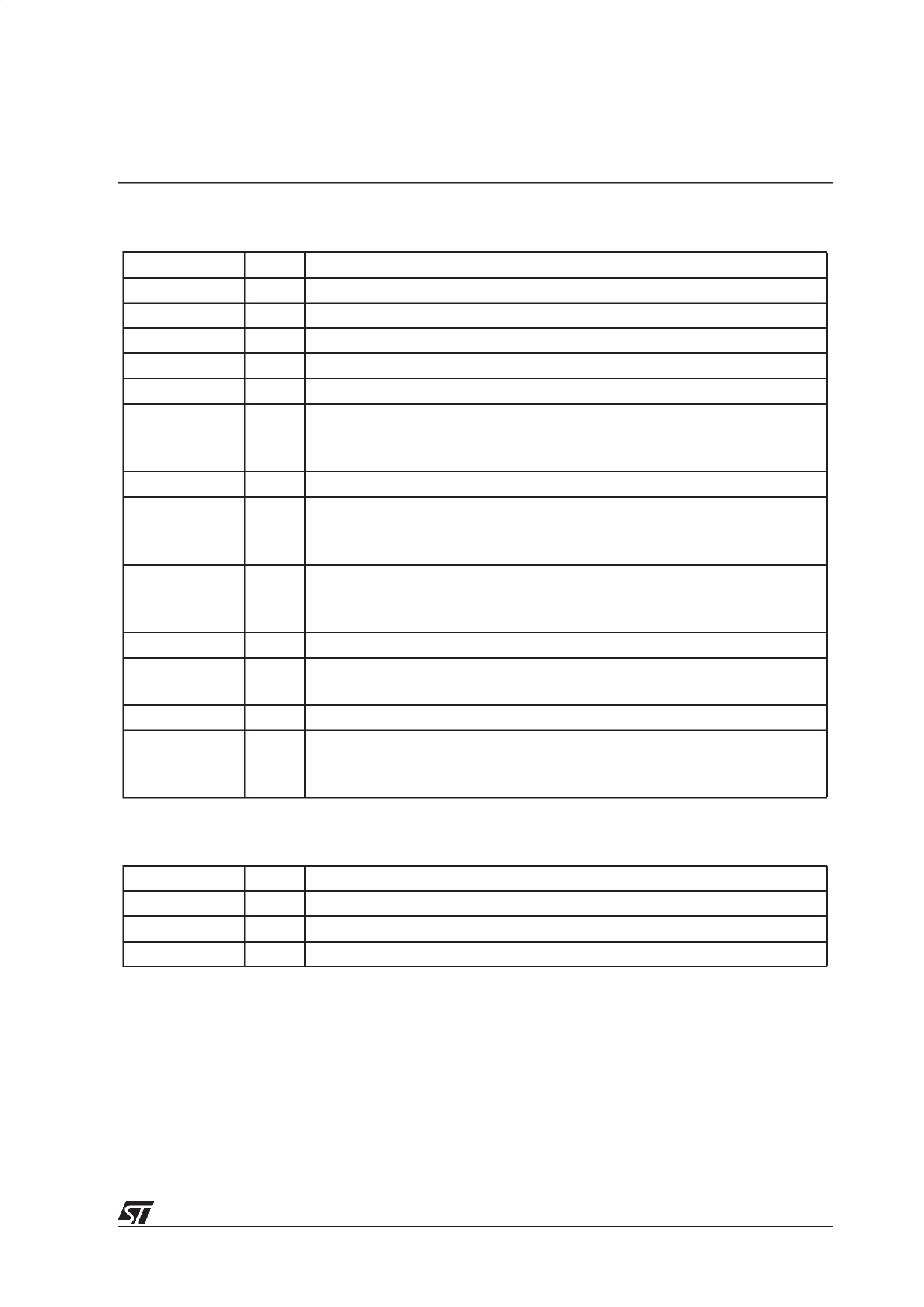

Table 2.4 Clocks (13 pins)

Pin name

EXTAL0

XTAL0

EXTAL1

XTAL1

CLK0

CLK0_MODE

CLK1

CLK1_MODE

PLL_MODE

CLKOUT

INCYCLE

SCLK

MCLK_MODE

Type

I

O

I

O

I

I

I

I

I

O

O

I/O

I

Description

Oscillator0 input. DSP PLL.

Oscillator0 output. Nominal oscillator frequency is 27 MHz.

Oscillator1 input. Audio PLL

Oscillator1 output. Nominal oscillator frequency is 27 MHz.

Direct clock input for D950 core.

Clock0 mode select input.

When low, select output of DSP PLL for DSP Clock In

When high, select CLK0 (bypass DSP PLL) for DSP Clock In

Direct audio clock input.

Clock1 mode select input.

When low, select output of audio PLL for audio clock

When high, select CLK1 (bypass audio PLL) for DSP Clock In

PLL mode select input

When low, select oscillator 1 for audio PLL

When high, select oscillator 0 for audio PLL

Output clock (at input clock/2 frequency).

Instruction cycle.

Asserted high for 1 CLKOUT cycle at the beginning of instruction cycle.

External audio clock/audio clock prescaler output

SCLK mode select input

When low, SCLK = output (internal audio master clock from clock prescaler)

When high, SCLK = input (external audio master clock)

Table 2.5 I2C Host interface (3 pins)

Pin name

HDA

HCL

HSAS

Type

I/O

/O

I

Description

I2C Data input/output (open drain output).

I2C Clock input/output (open drain output).

Slave address select

9/87