T431616D データシートの表示(PDF) - Taiwan Memory Technology

部品番号

コンポーネント説明

メーカー

T431616D Datasheet PDF : 74 Pages

| |||

tm TE

CH

T431616D/E

Commands

1 BankPrecharge command

(RAS# = "L", CAS# = "H", WE# = "L", A11 = “V”, A10 = "L", A0-A9 = Don't care)

The BankPrecharge command precharges the bank disignated by A11 signal. The precharged bank is

switched from the active state to the idle state. This command can be asserted anytime after tRAS(min.) is satisfied

from the BankActivate command in the desired bank. The maximum time any bank can be active is specified by

tRAS(max.). Therefore, the precharge function must be performed in any active bank within tRAS(max.). At the

end of precharge, the precharged bank is still in the idle state and is ready to be activated again.

2 PrechargeAll command

(RAS# = "L", CAS# = "H", WE# = "L", A11 = Don't care, A10 = "H", A0-A9 = Don't care)

The PrechargeAll command precharges both banks simultaneously and can be issued even if both banks are

not in the active state. Both banks are then switched to the idle state.

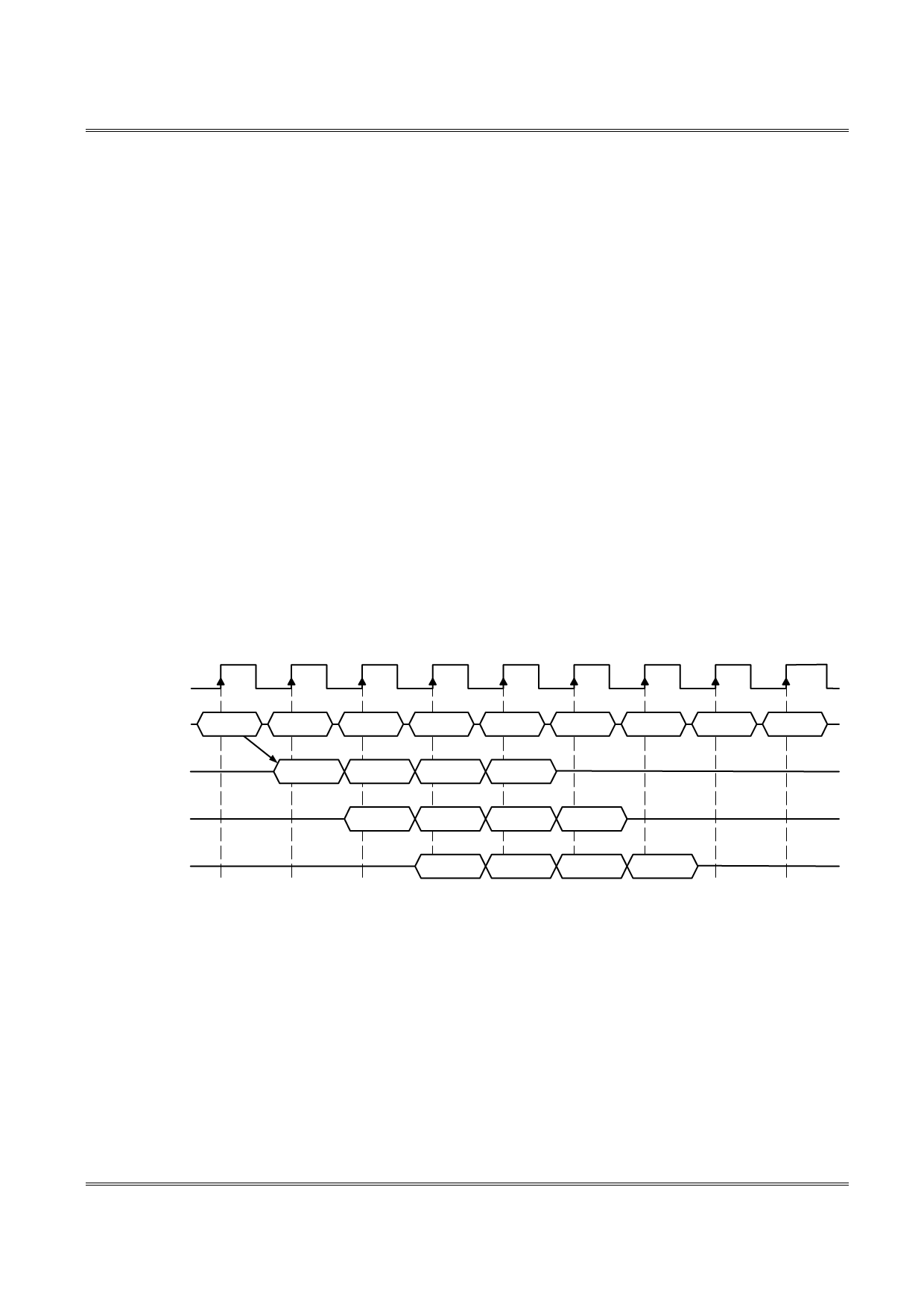

3 Read command

(RAS# = "H", CAS# = "L", WE# = "H", A11= “V”, A9 = "L", A0-A7 = Column Address)

The Read command is used to read a burst of data on consecutive clock cycles from an active row in an

active bank. The bank must be active for at least tRCD(min.) before the Read command is issued. During read

bursts, the valid data-out element from the starting column address will be available following the CAS# latency

after the issue of the Read command. Each subsequent data-out element will be valid by the next positive clock

edge (refer to the following figure). The DQs go into high-impedance at the end of the burst unless other

command is initiated. The burst length, burst sequence, and CAS# latency are determined by the mode register,

which is already programmed. A full-page burst will continue until terminated (at the end of the page it will wrap

to column 0 and continue).

T0

T1

T2

T3

T4

T5

T6

T7

T8

CLK

COMMAND

READ A

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

CAS# latency=1

tCK1, DQ's

DOUT A0 DOUT A1

DOUT A2 DOUT A3

CAS# latency=2

tCK2, DQ's

CAS# latency=3

tCK3, DQ's

DOUT A0 DOUT A1

DOUT A2 DOUT A3

DOUT A0 DOUT A1

DOUT A2 DOUT A3

Burst Read Operation(Burst Length = 4, CAS# Latency = 1, 2, 3)

TM Technology Inc. reserves the right

P. 6

to change products or specifications without notice.

Publication Date: FEB. 2007

Revision: A