TB62702F(2003) データシートの表示(PDF) - Toshiba

部品番号

コンポーネント説明

メーカー

TB62702F Datasheet PDF : 9 Pages

| |||

TB62702P/F

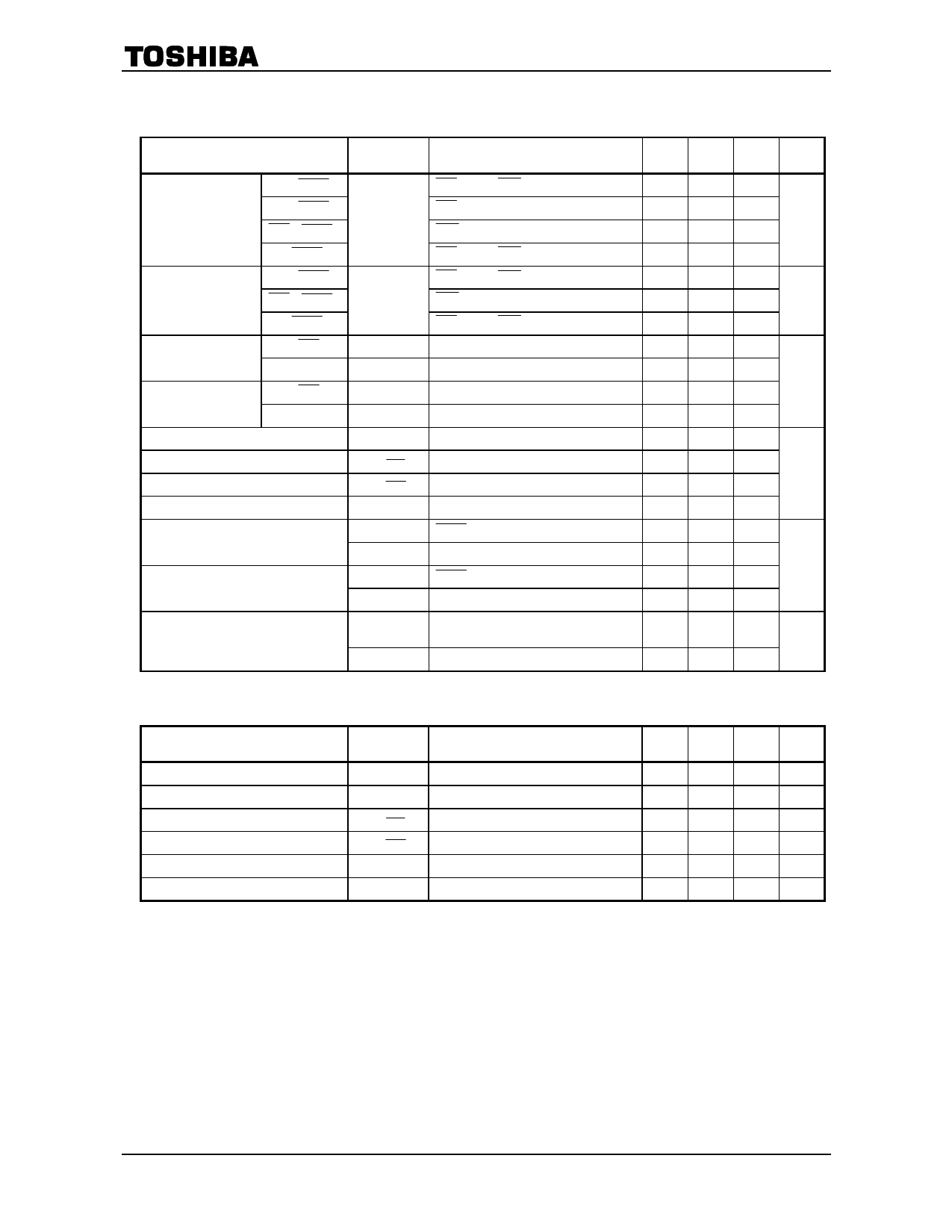

SWITCHING CHARACTERISTICS

(Ta = 25°C, VDD = 5 V, VOUT = 30 V, RL = 1150 Ω, CL = 15 pF, "H" = VIH, "L" = VIL)

CHARACTERISTIC

Propagation Delay

Time (Low−to−High)

Propagation Delay

Time (High−to−Low)

Set Up Time

Hold Time

Clock Pulse Width

Latch Pulse Width

Clear Pulse Width

Enable Pulse Width

CLK− OUTn

CLK− OUTn

LAT − OUTn

EN− OUTn

CLK− OUTn

LAT − OUTn

EN− OUTn

CLK− LAT

CLK−S−IN

CLK− LAT

CLK−S−IN

Output Rise Time

Output Fall Time

Maximum Clock Frequency

SYMBOL

TEST CONDITION

tpLH

tpHL

tsetup (L)

tsetup (D)

thold (L)

thold (D)

tw CLK

tw LAT

tw CLR

tw EN

tor

tr

tof

tf

fMAX1

fMAX2

LAT = "H", CLR = "H", EN = "H"

LAT = "H", EN = "H"

CLR = "H", EN = "H"

LAT = "H", CLR = ”H”

LAT = "H", CLR = "H", EN = "H"

CLR = "H", EN = "H"

LAT = "H", CLR = "H"

―

―

―

―

―

―

―

―

OUTn

S−OUT, VSS = 0V

OUTn

S−OUT, VSS = 0V

Duty = 50%

Cascade connected

Duty = 50%

MIN TYP. MAX UNIT

―

―

250

―

―

250

ns

―

―

200

―

―

150

―

―

250

―

―

200

ns

―

―

150

―

―

50

―

―

35

ns

―

―

105

―

―

50

―

―

100

―

―

50

ns

―

―

50

―

―

400

―

― 1000

―

―

50

ns

―

―

150

―

―

50

5

8

―

MHz

6

12

―

RECOMMENDED TIMING CONDITIONS (Ta = −40~85°C, VDD = 4.5~5.5 V, VSS = 0)

CHARACTERISTIC

Clock Pulse Width

Enable Pulse Width

Latch Pulse Width

Clear Pulse Width

Data Set Up Time

Data Hold Time

SYMBOL

tw CLK

tw EN

tw LAT

tw CLR

tsetup

thold

TEST CONDITION

―

―

―

―

―

―

MIN TYP. MAX UNIT

100

―

―

ns

400

―

―

µs

100

―

―

ns

100

―

―

ns

100

―

―

ns

150

―

―

ns

4

2003-05-14