A67L7336 データシートの表示(PDF) - AMIC Technology

部品番号

コンポーネント説明

メーカー

A67L7336 Datasheet PDF : 19 Pages

| |||

A67L8316/A67L8318/

A67L7332/A67L7336 Series

Pin Description (continued)

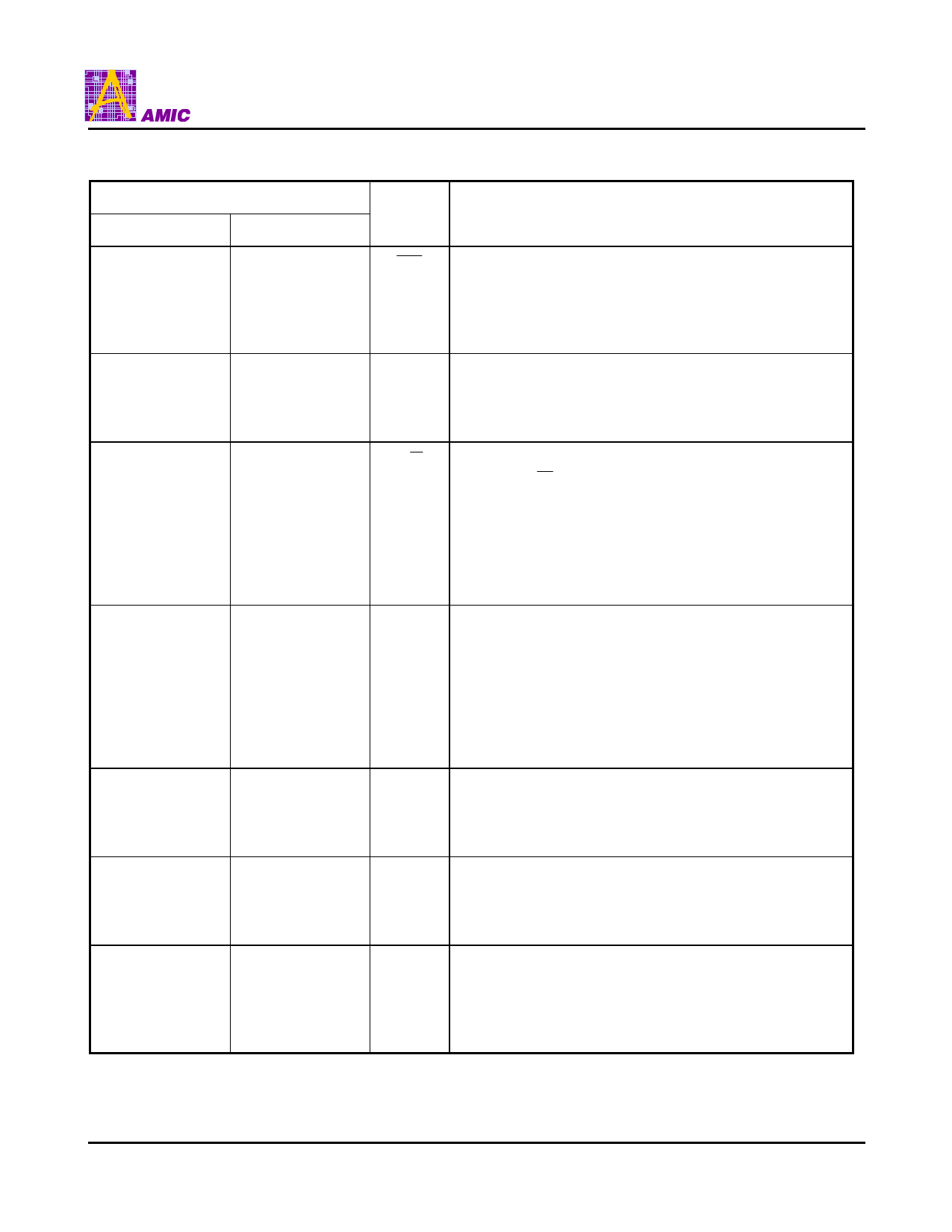

Pin No.

LQFP (X16/X18) LQFP (X32/X36)

87

87

64

64

88

88

(a) 58, 59, 62, 63,

68, 69, 72, 73

(b) 8,9,12,13, 18,

19, 22,23

74

24

31

(a) 52, 53, 56, 57,

58, 59, 62, 63

(b) 68, 69, 72, 73,

74, 75, 78, 79

(c) 2, 3, 6, 7, 8, 9,

12, 13,

(d) 18, 19, 22, 23,

24, 25, 28, 29

51

80

1

30

31

1, 2, 3, 6, 7, 25,

28, 29, 30, 38, 39,

42, 43, 51, 52, 53,

56, 57, 75, 78, 79,

83, 84, 95, 96

38,39,42,43

83,84

Symbol

CEN

ZZ

R/ W

I/Oa

I/Ob

I/Oc

I/Od

NC/I/Oa

NC/I/Ob

NC/I/Oc

NC/I/Od

MODE

NC

Description

Synchronous Clock Enable : This active low input permits

CLK to propagate throughout the device. When HIGH, the

device ignores the CLK input and effectively internally

extends the previous CLK cycle. This input must meet setup

and hold times around the rising edge of CLK.

Snooze Enable : This active high asynchronous input

causes the device to enter a low-power standby mode in

which all data in the memory array is retained. When active,

all other inputs are ignored.

Read/Write : This active input determines the cycle type

when ADV/LD is LOW. This is the only means for

determining READs and WRITEs. READ cycles may not be

converted into WRITEs (and vice versa) other than by

loading a new address. A LOW on this pin permits BYTE

WRITE operations and must meet the setup and hold times

around the rising edge of CLK. Full bus width WRITEs

occur if all byte write enables are LOW.

SRAM Data I/O : Byte “a”is I/Oa pins; Byte “b”is I/Ob pins;

Byte “c”is I/Oc pins; Byte “d”is I/Od pins. Input data must

meet setup and hold times around CLK rising edge.

No Connect/Data Bits : On the X16/32 version, these pins

are no connect (NC) and can be left floating or connected to

GND to minimize thermal impedance. On the X18/36

version, these bits are I/Os.

Mode : This input selects the burst sequence. A LOW on

this pin selects linear burst. NC or HIGH on this pin selects

interleaved burst. Do not alter input state while device is

operating.

No Connect : These pins can be left floating or connected to

GND to minimize thermal impedance.

PRELIMINARY (March, 1999, Version 0.0)

6

AMIC Technology, Inc.