UPD75048GC-XXX-AB8 データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

メーカー

UPD75048GC-XXX-AB8 Datasheet PDF : 68 Pages

| |||

µPD75048

(cont'd)

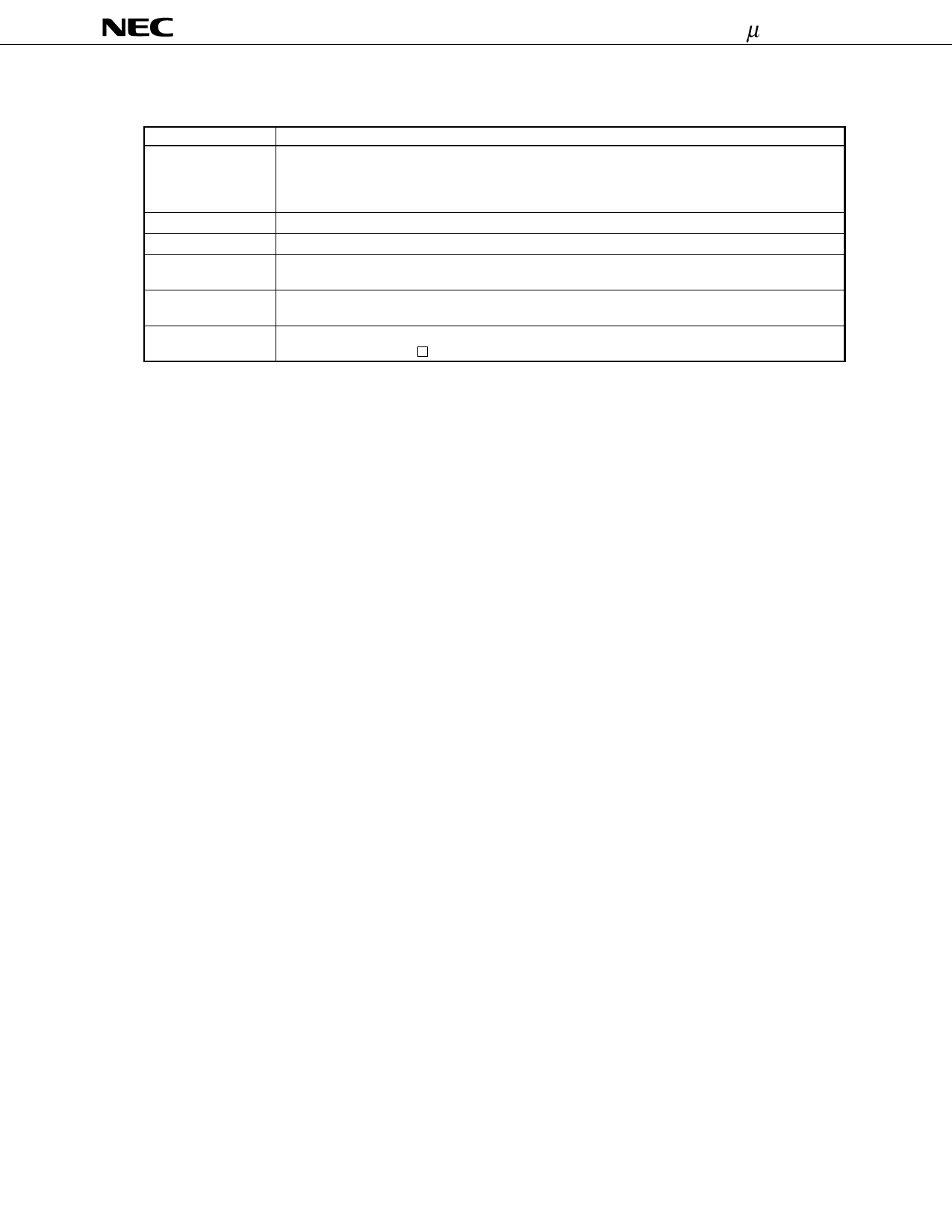

Item

A/D Converter

Vector Interrupt

Test Input

System Clock

Oscillator Circuit

Standby Function

Package

Function

8-bit resolution A/D converter (successive approximation type): 8 channels

• Low-voltage operation: VDD = 2.7 – 6.0 V

• Reference voltage setting range: AVREF+ – AVREF–

2.5 V ≤ (AVREF+) – (AVREF–) ≤ 6.0 V

External: 3, Internal: 6

External: 1, Internal: 1

• Ceramic/crystal oscillator circuit for main system clock oscillation

• Crystal oscillator circuit for subsystem clock oscillation

• STOP mode: main system clock oscillation stops

• HALT mode: system clock oscillation continues (clock supply to CPU stops)

• 64-pin plastic shrink DIP (750 mil)

• 64-pin plastic QFP ( 14 mm)

3