UPD75212ACW データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

メーカー

UPD75212ACW Datasheet PDF : 70 Pages

| |||

µPD75212A

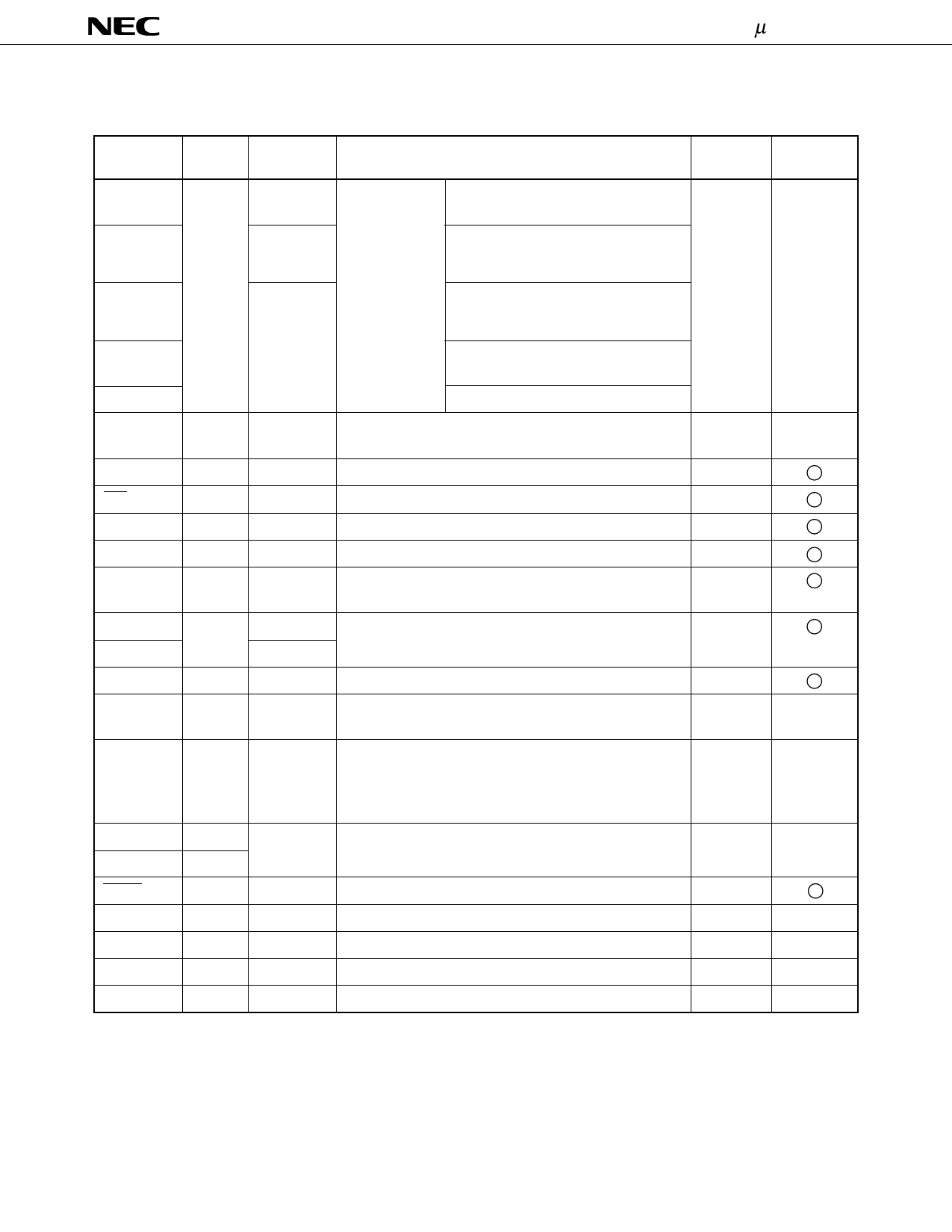

3.2 NON-PORT PINS

Pin Name

T0 to T9

T10/S15 to

T13/S12

T14/S11,

T15/S10

Dual-

I/O

Function Pin

Function

Input / Output

After Reset Circuit Type *

Output

–––

FIP controller/ Digit output high-voltage high-current Low level

I

PH3 to PH0

–––

driver output

pins.

Pull-down

resistor can be

incorporated in

bit-wise (mask

option).

output.

Digit/segment output dual-function

high-voltage high-current output.

Extra pins can be used as PORTH.

Digit/segment output dual-function

high-voltage high-current output.

Static output also possible.

(With an on-

chip pull-

down

resistor) or

high

impedance

(without a

pull-down

resistor)

S9

Segment output high-voltage output.

Static output also possible.

S0 to S8

Segment high-voltage output.

PPO

Output

–––

Timer/pulse generator pulse output.

High

D

impedance

TI0

Input

P13

External event pulse input for timer/event counter.

B

SCK

Input/output

P01

Serial clock input/output.

Input

F

SO

Input/output

P02

Serial data output pin or serial data input/output.

Input

G

SI

INT4

Input

P03

Serial data input or normal input.

Input

B

Input

P00

Edge-detected vectored interrupt input (rising and falling

B

edge detection).

INT0

Input

P10

Edge-detected vectored interrupt input with noise

B

INT1

elimination function (detection edge selection possible).

P11

INT2

Input

P12

Edge-detected testable input (rising edge detection).

B

BUZ

Input/output

P23

Fixed frequency output (for buzzer or system clock

Input

E

trimming).

X1, X2

Input

–––

Crystal/ceramic connect pin for main system clock

oscillation.

External clock input to X1 and its inverted clock input to

X2.

XT1

Input

–––

Crystal connect pin for subsystem clock oscillation.

XT2

–––

External clock input to XT1 and XT2 open.

RESET

Input

–––

System reset input (low level active).

B

VPRE

–––

FIP controller/driver output buffer power supply.

I

VLOAD

–––

FIP controller/driver pull-down resistor connect pin.

I

VDD

–––

Positive power supply.

VSS

–––

GND potential.

* Schmitt-triggered inputs are circled.

10