VSC870 データシートの表示(PDF) - Vitesse Semiconductor

部品番号

コンポーネント説明

メーカー

VSC870 Datasheet PDF : 40 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

High Performance Serial

Backplane Transceiver

Data Sheet

VSC870

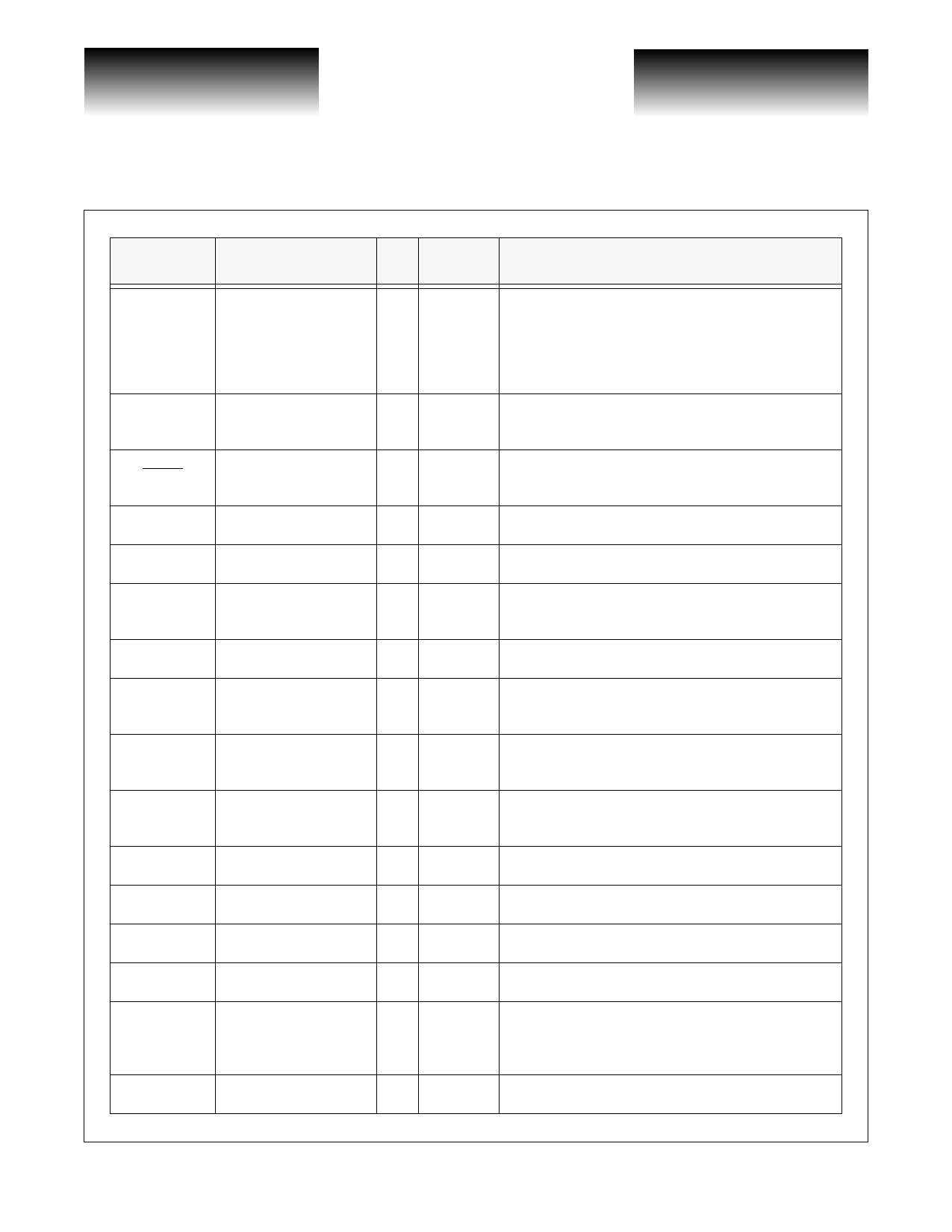

Symbol

Name

I/O

Freq

Type

Description

RXSEL

Receive Input Select

When RXSEL is LOW and LOOPBACK is LOW, RXSA

is selected as the input to the CRU and RXSB is selected

I

<1MHz

TTL

as the input to the Signal Detector. When RXSEL is

HIGH and LOOPBACK is LOW, RXSB is selected as the

input to the CRU and RXSA is selected as the input to the

Signal Detector.

ALIVE

Redundant Input Alive O

<1MHz

TTL

This output is high if at least one edge transition is

detected every word clock period on the redundant input

serial line.

RXOK

Receive Signal OK

O

<1MHz

TTL

This signal goes LOW if the VSC870 is word aligned on

the receive side. After initialization, it goes HIGH if there

is error in the IDLE words.

RXEN

Receive Enable

I

62.5Mb/s When RXEN is LOW, the RXOUT[31:0] and

TTL RXTYP[1:0] outputs become high impedance.

RXOUT[31:0]

Receive Parallel Data

Out

O

62.5Mb/s

TTL

32-bit parallel data output for the receive side.

RXTYP[1:0]

Receive Word Type

O

62.5Mb/s

TTL

If BYPASS is LOW, these signals tell the received word

type. If BYPASS is HIGH, these signals reflect the

overhead bits received on the serial channel.

RXWA

Receive Word Available

O

62.5Mb/s When RXWA is LOW, RXTYP[1:0] and RXOUT[31:0]

TTL is an IDLE word.

ACK/RCLK

Acknowledge /

Receive Cell Clock

O

62.5Mb/s

TTL

In Packet Mode, the ACK signal will be set high if a

Connection Request on the transmit side is granted. In

Cell mode, a high pulse represents the receive cell clock.

ABORT

Connection Request

Abort

I

62.5Mb/s

TTL

When BYPASS is LOW and ABORT is HIGH, the

connection request and data transmission process is

aborted.

WSIN

Word Synch In

I

62.5MHz

TTL

The WSIN signal provides the word clock input and must

be driven by a signal frequency locked to the WSOUT

signal either from itself or another transceiver.

WSOUT

Word Synch Out

O

62.5MHz The WSOUT signal is the internally generated word clock

TTL

and is synchronized to the transmit word clock.

RESYNEN

Resync Enable

I

<1MHz

TTL

If RESYNEN is HIGH and the transceiver detects a link

error, it will start the Link Initialization process.

OOS

Out Of Sync

O

<1MHz

TTL

If OOS is HIGH, the transceiver is in the link

initialization process. It is LOW during normal operation.

SCRAM

Scramble Enable

I

<1MHz

TTL

If SCRAM is HIGH, data words will be scrambled and

descrambled.

BYPASS

Bypass Mode

BYPASS is set HIGH for direct control and monitoring of

I

<1MHz

TTL

the overhead bits in the serial data streams as in cell mode

and direct mode. This also disables the transceiver Packet

Mode functions.

CELLSYN

Cell Synchronization

Enable

I

<1MHz

TTL

CELLSYN is set HIGH to allow cell synchronization

during link initialization.

Page 4

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

G52190-0, Rev 4.1

01/05/01